下一代射频芯片,靠它们了

来源:imec

年复一年,越来越多的用户通过无线方式传输越来越多的数据。为了跟上这一趋势并使数据传输更快、更高效,第五代移动通信 (5G) 正在推出,业界已经在关注未来的发展。5G 可实现 10Gbit/s 的峰值数据速率,而 6G 预计从 2030 年起将以 100Gbit/s 的速度运行。除了应对更多数据和连接之外,研究人员还研究下一代无线通信如何支持自动驾驶和全息存在等新用例。

为了实现极高的数据速率,电信行业一直在提高无线信号的频率。虽然 5G 最初使用 6GHz 以下频段,但针对 28/39GHz 的产品已经展示。此外,由于 FR3 (6-20GHz) 频段能够平衡覆盖范围和容量,因此人们对 5G 网络使用 FR3 (6-20GHz) 频段越来越感兴趣。对于 6G,100GHz 以上的频率正在讨论中。

转向更高的频率有几个优点:可以使用新的频段,解决现有频段内的频谱稀缺问题。而且,工作频率越高,就越容易获得更宽的带宽。原则上,高于 100GHz 的频率和高达 30GHz 的带宽允许电信运营商在无线数据链路中使用低阶调制方案,从而降低功耗。较高的频率还与较小的波长 (λ) 相关。随着天线阵列尺寸随λ 2缩放,天线阵列可以排列得更密集。这有助于更好的波束成形,这种技术可确保大部分传输能量到达目标接收器。

但更高频率的出现是有代价的。如今,CMOS是构建****和接收器关键组件的首选技术。其中包括前端模块内的功率放大器,用于向天线发送射频信号或从天线发送射频信号。工作频率越高,基于 CMOS 的功率放大器就越难以以足够高的效率提供所需的输出功率。

这就是GaN 和 InP等技术发挥作用的地方。由于出色的材料特性,这些 III/V 族半导体更有可能在高工作频率下提供所需的输出功率和效率。例如,GaN具有高电流密度、高电子迁移率和大击穿电压。高功率密度还可以实现较小的外形尺寸,从而在相同性能的情况下减小总体系统尺寸。

GaN 和 InP 在更高的工作频率下优于 CMOS

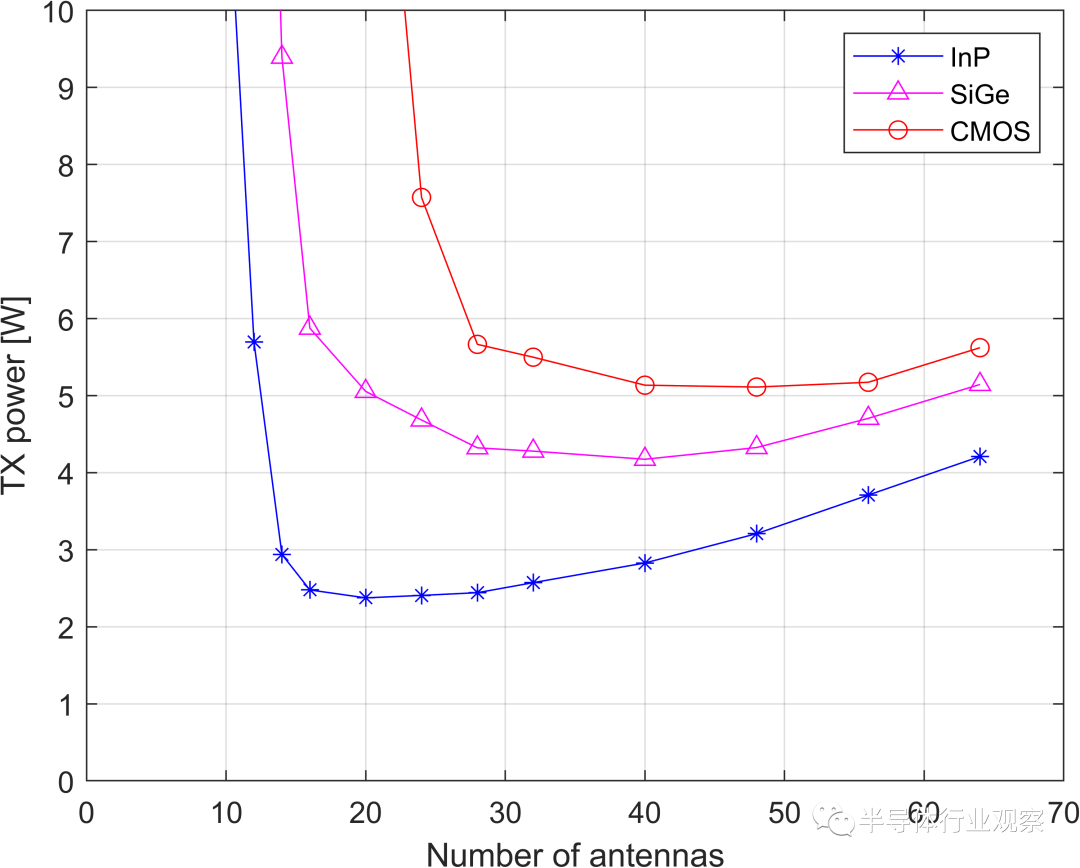

在建模实验中,imec 的研究人员比较了140GHz工作频率下三种不同功率放大器实现的性能:全 CMOS 实现、带有 SiGe 异质结双极晶体管 (HBT) 的 CMOS 波束形成器(beamformer)和InP HBT。InP 在输出功率(超过 20dBm)和能源效率(20% 至 30%)方面明显获胜。建模结果还表明,对于 InP,能量效率的最佳点是通过相对较少的天线数量获得的。这对于用户设备(例如移动设备)等占地面积受限的用例尤其有趣。

图 1 – 比较****架构中 CMOS、SiGe 和 InP 器件的功耗与天线数量的关系(如 IEDM 2022 上所述)。

然而,在较低的毫米波频率下,GaN表现出优异的性能。对于28GHz 和 39GHz,由碳化硅上氮化镓 (GaN-on-SiC) 制成的高电子迁移率晶体管 (HEMT) 在输出功率和能效方面均优于基于 CMOS 的器件和 GaAs HEMT。考虑了两种不同的用例,即固定无线接入(FWA,具有 16 个天线)和用户设备(具有 4 个天线)。

图 2 –(左)FWA 和(右)用户设备中 28GHz 和 39GHz 工作频率的输出功率:三种不同技术的比较(如 IEDM 2022 上所示)。

升级的机遇与挑战

但如果我们考虑成本和集成的简易性,GaN 和 InP 器件技术还无法与基于 CMOS 的技术完全竞争。III/V 器件通常在小型且昂贵的非硅衬底上制造,依赖于不太适合大批量制造的工艺。将这些器件集成在 200 或 300mm 硅晶圆上是一种有趣的方法,可以在保持卓越射频性能的同时实现整体优化。硅基板不仅更便宜,而且兼容 CMOS 的工艺还可以实现大规模制造。

在 Si 平台上集成 GaN 和 InP需要结合新的晶体管和电路设计方法、材料和制造技术。主要挑战之一与大晶格失配有关:InP 为 8%,GaN 为 17%。众所周知,这会在层中产生许多缺陷,最终降低器件性能。

此外,我们还必须将基于 GaN-on-Si 和 InP-on-Si 的组件与基于 CMOS 的组件共同集成到一个完整的系统中。GaN 和 InP 技术最初将用于实现前端模块内的功率放大器。此外,低噪声放大器和开关可能受益于这些化合物半导体的独特性能。但最终,校准、控制和波束形成仍然需要 CMOS。

在其高级射频计划中,imec 与其行业合作伙伴一起探索在大尺寸硅晶圆上集成 GaN 和 InP 器件的各种方法,以及如何实现它们与 CMOS 组件的异构集成。正在评估不同用例(基础设施(例如 FWA)以及用户设备)的优缺点。

改进 GaN-on-Si 技术的射频性能

根据起始衬底的不同,GaN 技术有多种类型:GaN bulk substrates, GaN-on-SiC和GaN-on-Si。如今,GaN-on-SiC得到了广泛探索,并已用于基础设施应用,包括 5G ****。GaN-on-SiC比GaN bulk substrates技术更具成本效益,而且碳化硅是一种出色的热导体,有助于散发高功率基础设施应用中产生的热量。然而,成本和基板尺寸有限使其不太适合大规模生产。

相反,GaN-on-Si具有扩大到 200mm 甚至 300mm 晶圆的潜力。得益于多年来电力电子应用的创新,GaN在大尺寸Si衬底上的集成取得了巨大进展。但硅基氮化镓技术还需要进一步改进,以实现最佳射频性能。主要挑战在于实现与 GaN-on-SiC 相当的大信号和可靠性性能以及提高工作频率。这需要在材料堆叠设计和材料选择方面不断创新,缩短 HEMT 的栅极长度,抑制寄生效应,并保持尽可能低的射频色散。

Imec 的射频 GaN-on-Si 工艺流程从在 200mm Si 晶圆上生长(通过金属有机化学气相沉积 (MOCVD))外延结构开始。该结构由专有的 GaN/AlGaN 缓冲结构、GaN 沟道、AlN 间隔物和 AlGaN 势垒组成。具有 TiN 肖特基金属栅极的 GaN HEMT 器件随后与(低温)3 级 Cu 后道工艺集成。

近期,imec的GaN-on-Si平台取得了具有竞争力的成果,输出功率和功率附加效率(PAE)首次接近GaN -on-SiC技术。PAE 是评估功率放大器效率的常用指标,它考虑了放大器增益对其整体效率的影响。

图 3 - 硅基氮化镓基准测试数据。红色的 IMEC 数据是 GaN-on-Si 器件的最佳报告之一,可与 GaN-on-SiC 衬底相媲美(如 IEDM 2022 上介绍的)。

通过建模活动补充技术开发将最终有助于实现更好的性能和可靠性。例如,在 IEDM 2022 上,imec 推出了一个仿真框架,可以更好地预测射频设备中的热传输。在硅基氮化镓 HEMT 的案例研究中,模拟显示峰值温升比之前预测的高出三倍。诸如此类的建模工作为在开发阶段早期优化射频器件及其布局提供了进一步的指导。

用于 6G 亚太赫兹频率的 InP-on-Si:三种制造方法

如前所述,InP HBT在所有技术实现的140GHz工作频率下提供最佳输出功率/效率权衡。研究人员还知道如何设计 InP HBT 以获得最佳射频性能。但制造通常从小型 (InP) 衬底晶圆 (< 150mm) 开始,使用与CMOS 不兼容的类似实验室的工艺。

但是当我们在 Si 上集成 InP 时,性能会发生什么变化呢?众所周知,在 Si 上沉积 InP 会引入许多缺陷,主要是螺纹位错( threading dislocations)和平面缺陷(planar defects)。这些缺陷会引起漏电流,从而极大地降低器件性能或导致可靠性问题。

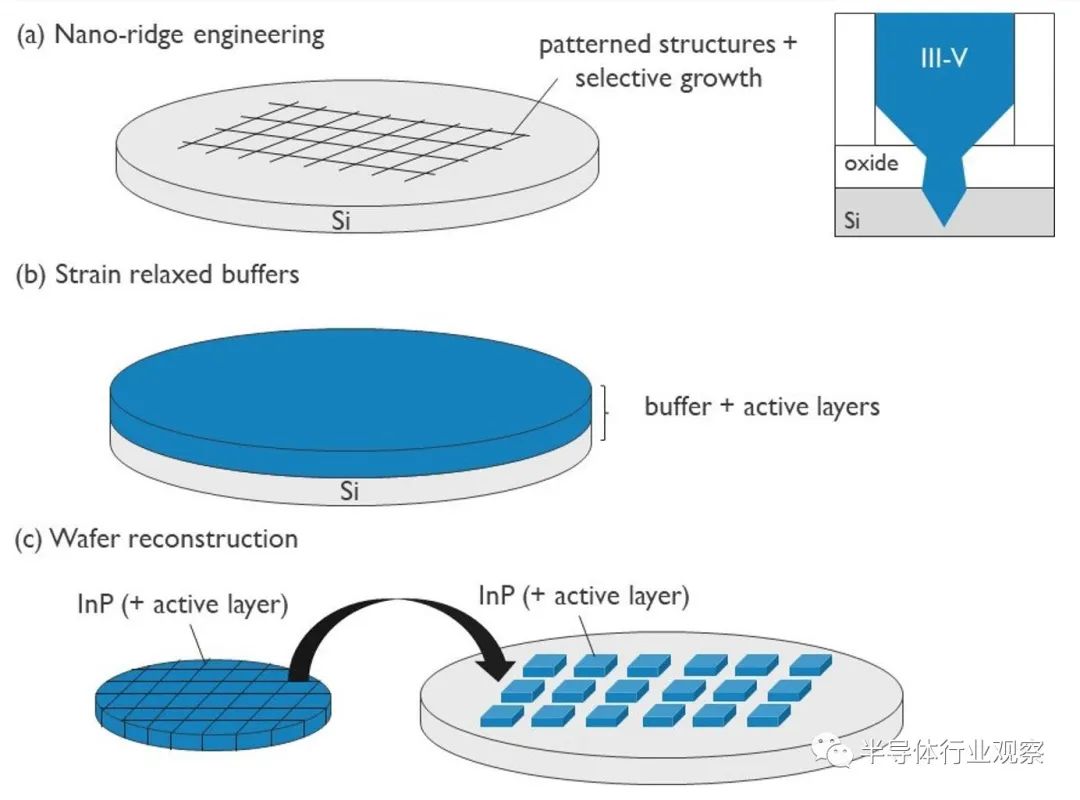

正在考虑三种升级方法。其中两个依赖于 Si 上 InP 的直接生长,另一个依赖于晶圆重构。预计所有三种方法都将提供比使用小型 InP 衬底的现有技术更具成本效益的解决方案。但它们在性能、成本和异构集成潜力方面都各有利弊。Imec 承担了评估各种用例(基础设施以及移动设备)的优势和挑战的角色。

图 4 – 不同 InP-on-Si 生长方法的示意图:(a) nano-ridge engineering; (b) blanket growth with strain relaxed buffers, and (c) wafer reconstruction.

制造 InP-on-Si HBT 的第一种方法(图 4b)使用直接沉积在 Si 顶部的应变松弛缓冲层,以补偿 Si 和 InP 之间 8% 的晶格失配。接下来,InP直接生长在该缓冲层的顶部。使用更大晶圆尺寸的能力,特别是在部分硅可以重复使用的情况下,提供了显着的成本优势。然而,需要优化以进一步减少缺陷数量。

与这种“blanket”生长方法不同,imec 提出nano-ridge engineering(NRE) 作为更有效地应对缺陷的替代技术(图 4a)。NRE 依赖于在 Si 中预先图案化的沟槽中选择性生长 III/V 族材料。这些高深宽比沟槽对于捕获狭窄底部中的缺陷非常有效,并允许在沟槽外生长高质量、低缺陷率的材料。过度生长的nano-ridge使其向顶部变宽,为设备堆栈形成坚实的基础。从 GaAs/InGaP 案例研究中获得的初步见解将指导目标 InGaAs/InP NRE HBT 器件的优化。

除了直接生长之外,InP 还可以使用晶圆重建技术放置在 Si 上(图 4c)。在这种情况下,高质量 InP 衬底(无论是否有有源层)在晶圆构造过程中被切成片。随后使用芯片到晶圆键合技术将这些瓦片附着到硅晶圆上。主要挑战在于材料的有效转移和 InP 衬底的去除,为此正在考虑多种技术。

走向异构集成

最终,III/V-on-Si 功率放大器必须与负责校准和控制等功能的基于 CMOS 的组件相结合。Imec 正在研究各种异构集成选项,权衡它们在各种用例中的优缺点。

先进的层压基板技术是将不同射频元件集成到系统级封装中的最常见方法,并且正在进行优化以使其能够适应更高的频率。

此外,imec还探索更先进的异构集成选项,包括2.5D中介层和3D集成技术。

特别是对于 100GHz 以上的频率,需要注意的是天线模块开始定义收发器可用的区域。事实上,当频率较高时,波长会减小,天线阵列的面积也会相应缩小。在 100GHz 以上,天线尺寸变得小于前端模块尺寸,而前端模块尺寸几乎不会随着频率的增加而缩小。对于大型天线阵列配置,一个有趣的选择是将射频前端模块移至天线阵列下方。这就是3D 集成技术的用武之地(die-to-wafer or 和wafer-to-wafer)发挥作用,实现前端模块和天线模块之间的短且明确的连接。然而,热管理仍然是 3D 集成的一个重要问题,并且能够提供有效的散热器至关重要。在imec,我们正在进行全面的系统技术协同优化 (STCO) 分析,以评估用于 3D 集成的不同技术,并从系统级角度指导技术选择。

对于手持设备,减少天线数量可以放松限制,2.5D interposer技术被认为是一种有趣的方法。这种异构集成选项使用具有光刻定义连接的层堆栈,甚至是硅通孔,以在基于 III/V 和 CMOS 的组件之间进行通信。在这种情况下,III/V 器件位于 CMOS 芯片旁边,可以实现更好的热管理,因为两个芯片都可以与散热器直接接触。然而,这种架构仅允许一维波束控制。我们目前正在评估 2.5D 中介层技术的硬件实现,研究基板、电介质和再分布层的最佳组合,以最大限度地减少损耗。例如,我们展示了射频定制硅中介层技术的第一个版本,该技术使用标准硅基板、铜半加成互连、

图 75– 封装中集成有 InP 和 CMOS 器件以及天线阵列的 RF Si 内插器的示意图。

总之,最近的升级和集成工作表明,硅基氮化镓和硅基磷化铟可以成为下一代高容量无线通信应用的可行技术。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。