设计一颗2nm芯片,至少要7.25亿美元!

来源:半导体行业观察(ID:icbank)

近日,Marvell高管在一场分析会上表示,随着制程工艺的演进,芯片的研发成本正在飙升。

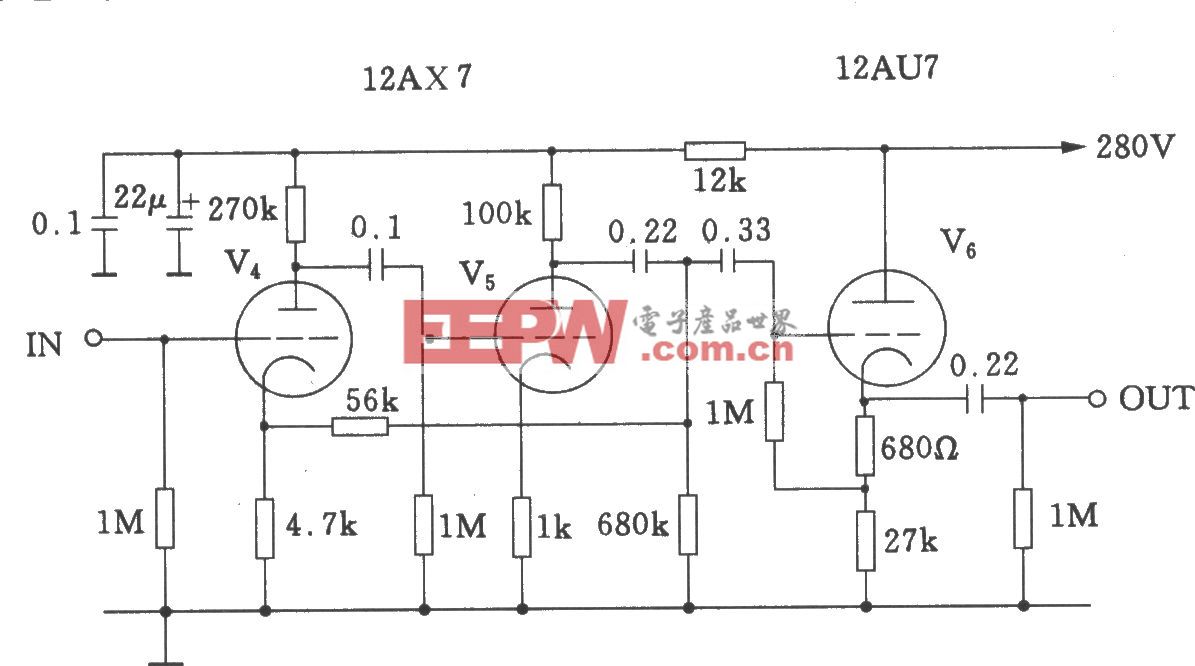

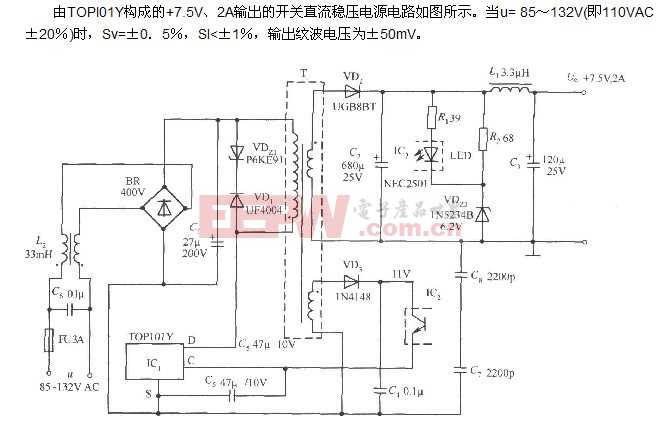

如下图所示,在28nm的时候,设计一颗芯片的成本仅为4280万美元。在接下来的的22和16nm,芯片设计成本有稳步上升,但幅度还是可控。到了10nm一下,芯片成本则同步飙升。

芯片工艺越来越先进了,今年三星量产了3nm工艺,台积电的3nm也是箭在弦上了,明年就会是3nm的高光时代,2024到2025年则是2nm工艺量产。

先进工艺生产出来的芯片性能更强大,能效也更好,但这也不是没有代价的,最大的麻烦就是烧钱,不仅是3nm、2nm工厂建设需要200亿美元以上的资金,哪怕是AMD、NVIDIA、苹果、高通这样的芯片设计公司,开发一款芯片的成本也会越来越高。

在前不久的IEDM会议上,Marvell公司公布了一些数据,援引IBS机构分析了各个工艺下芯片开发成本,其中28nm工艺只要4280万美元,22nm工艺需要6300万美元,16nm工艺需要8960万美元。

后面的先进工艺开发成本就直线上涨,7nm需要2.486亿美元,5nm需要4.487亿美元,3nm需要5.811亿美元,而2nm工艺需要的开发资金是7.248亿美元,人民币约合50亿。

换句话说,如果某家公司想要自己搞一款先进工艺芯片,比如2nm处理器,不说设计周期要几年时间,光是投入的资金就得50亿元。

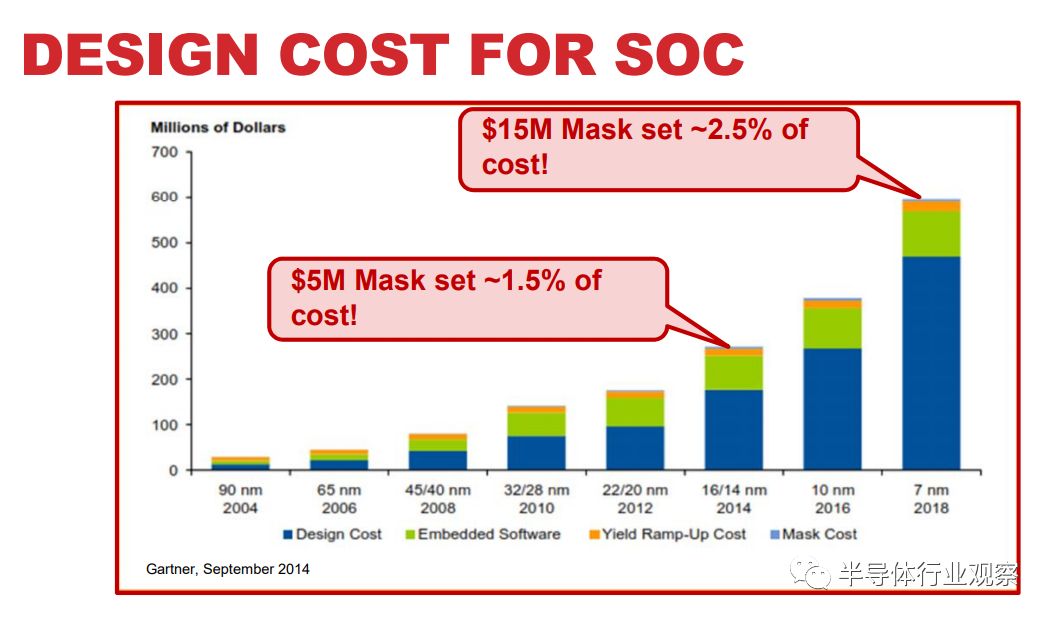

还不算生产的费用,2nm代工价格现在还没有,但是3nm工艺就要2万美元以上了,涨价25%。

照这样发展下去,未来2nm的CPU及显卡就算能做出来,成本也会一路上涨,在这个方向上已经没有退路了。

在笔者看来,按照这个增长幅度,芯片设计成本突破10亿美元指日可待。

从Marvell分享的这个图我们可以看到,在芯片设计成本中,软件占了大头,紧随其后的是Verification、Validation、physicical、IP qualification、prototype和architecture。按照上头的展示,本来在28nm的时候,软件就是芯片设计的最巨大的成本,但这种情况在22nm和16nm的时候被扭转了。但进入到了10nm以后,这种情况重新出现。由此可以看到先进工艺给芯片设计产业带来的挑战。

先进制程芯片成本为啥这么贵?

- 晶圆代工成本

根据CEST的模型,在5nm节点上构建的单个300mm晶圆的成本约为16988美元,在7nm节点上构建的类似晶圆成本为9346美元。可以看到,相同尺寸晶圆,5nm工艺节点相比7nm每片晶圆代工售价高7000多美元。

按节点计算2020年每个芯片的代工销售价格(图源:CSET)

按节点计算2020年每个芯片的代工销售价格(图源:CSET)从中可以推断出,在3nm节点上构建的晶圆成本或将达到3万美元左右,晶圆代工成本将进一步提高。

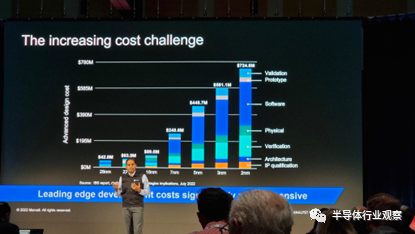

另一组数据也对此进行了印证,成本价格在很大程度上取决于芯片制程和晶圆尺寸的不同。IC Insights提供的数据显示,每片0.5µ 200mm晶圆代工收入(370美元)与≤20nm 300mm晶圆的代工收入(6050美元)之间相差超过16倍。即使同样是在300mm晶圆尺寸下,≤20nm 相比28nm工艺,成本相差也达到一倍。

2018年主要技术节点和晶圆尺寸的每片晶圆代工收入(图源:IC Insights)

2018年主要技术节点和晶圆尺寸的每片晶圆代工收入(图源:IC Insights)可见,随着工艺节点的提升,晶圆代工成本随之大幅度提升。

- 掩膜(Mask)成本

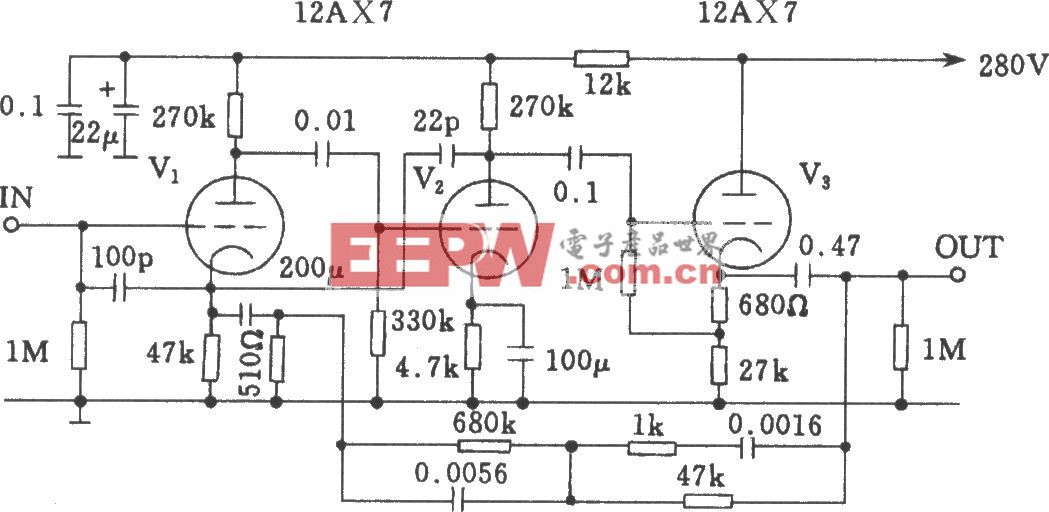

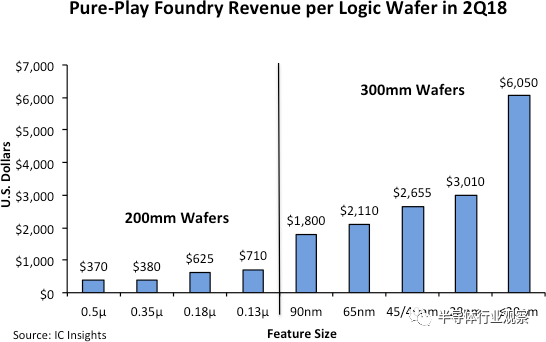

据IBS数据显示,在16/14nm制程中,所用掩膜成本在500万美元左右,到7nm制程时,掩膜成本迅速升至1500万美元。

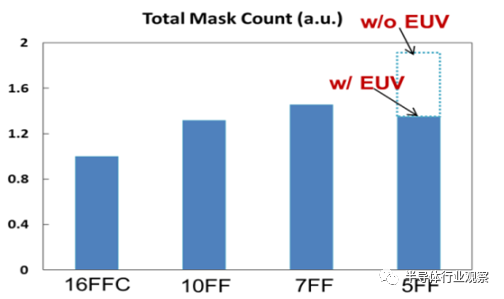

又从台积电(IEDM 2019)了解到,从10nm到5nm,随着EUV光刻技术的应用,掩膜使用数量有所减少,5nm与10nm制程中掩膜使用数量相差不多。

不同制程中的Mask数量(图源:台积电)

不同制程中的Mask数量(图源:台积电)但是,在掩膜数量基本持平的情况下,更先进的制程工艺使得掩膜总成本提升,能侧面反映出掩膜平均成本在不断升高。

再反映到芯片成本上,每片CPU的掩膜成本等于掩膜总成本/总产量。如果总体产量小,芯片的成本会因为掩膜成本而较高;如果产量足够大,比如每年出货以亿计,掩膜成本被巨大的产量分摊,可以使每块CPU的掩膜成本大幅降低,使拥有“更贵的制程工艺+更大的产量”属性的CPU,比“便宜的制程工艺+较小的产量”的CPU成本更低。

可以预见,到3nm时,掩膜成本预计将会再度攀升,进一步增加芯片成本。

- EUV光刻机

随着工艺制程的发展,到7nm及更先进的技术节点时,需要波长更短的极紫外(EUV)光刻技术来实现更小的制程。荷兰ASML是全球唯一有能力制造EUV光刻机的厂商。

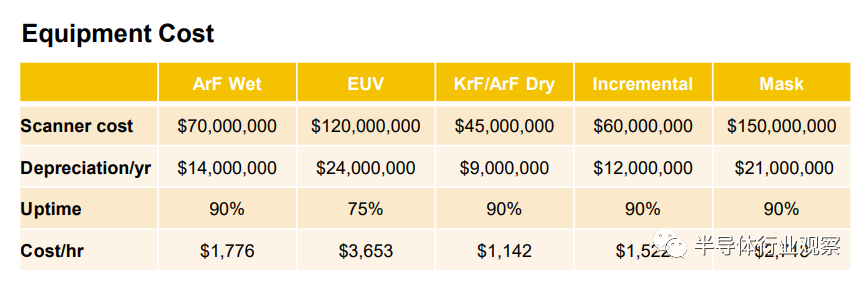

但EUV光刻机的价格一直以来十分昂贵,2018年,中芯国际和ASML签订了订购协议,以1.2亿美元的价格订购了一台EUV光刻机。这一价格与PHOTRONICS披露的EUV光刻机价格基本吻合。

设备成本(图源:PHOTRONICS)

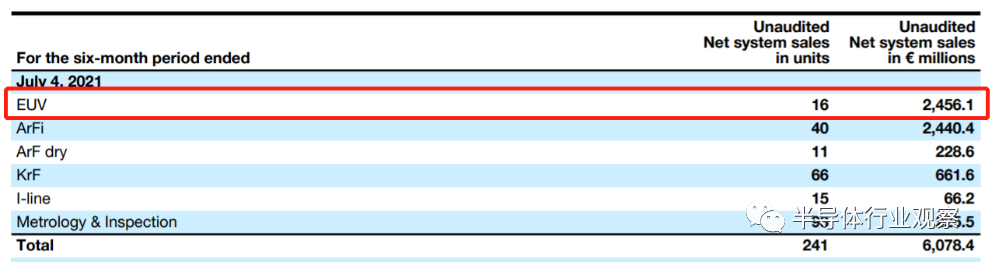

设备成本(图源:PHOTRONICS)从ASML最新公布的2021年第二季度财报来看,截止2021年7月4日,ASML今年出货EUV光刻机16台,销售额达到24.561亿欧元,平均每台EUV光刻机价格高达1.535亿欧元。

ASML 2021年Q2财报(图源:ASML)

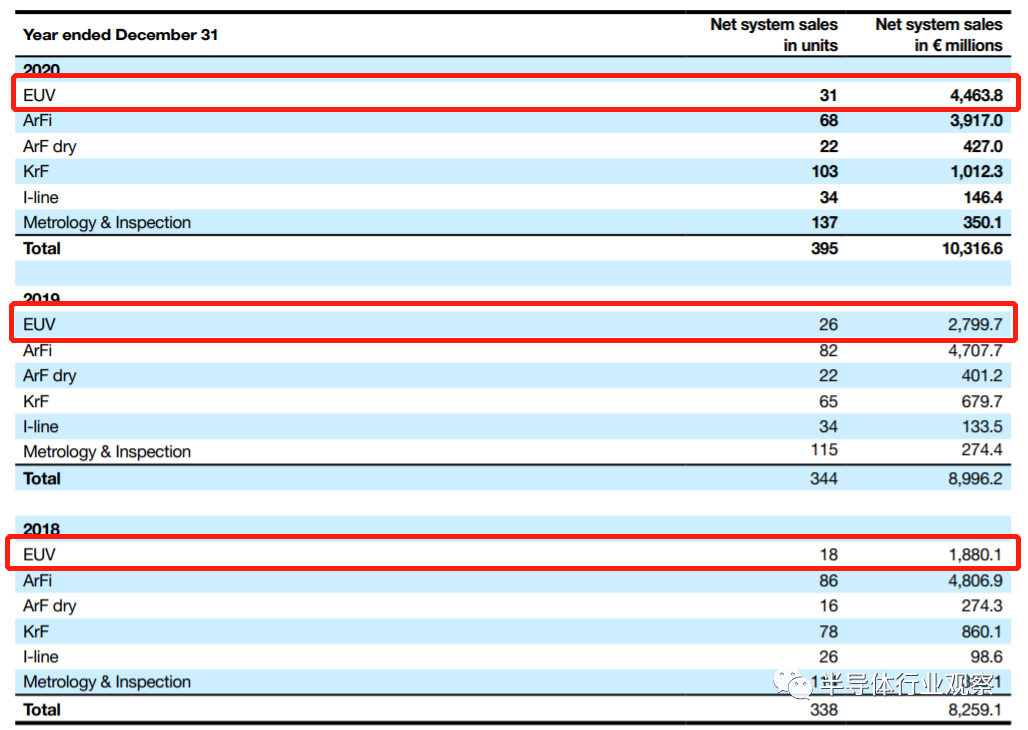

ASML 2021年Q2财报(图源:ASML)再结合ASML历年(2018/2019/2020三年)财报数据,能够看到ASML的EUV光刻机单从1.045亿欧元到1.44亿欧元,价格逐年攀升。

ASML 近三年财报(图源:ASML)

ASML 近三年财报(图源:ASML)一台EUV光刻机售价超过1亿美元,而且还相当不好买。ASML每推出一代EUV光刻机,新设备的生产能力在稳步提升,但价格自然更高。据披露,ASML第二代EUV光刻机将会是NXE:5000系列,进一步提高光刻精度,原计划2023年问世,现推迟到2025-2026年,而价格预计将突破3亿美元。

当然,除了价格最贵的EUV光刻机之外,沉积、刻蚀、清洗、封装等环节所采用的设备和材料也价格不菲,且成本都在随着工艺制程向前发展不断提高。

- 研发&人力成本

先进制程不仅需要巨额的建设成本,高昂的研发和人力费用也提高了设计企业的门槛。

人力成本是研发成本的重要部分,项目开发效率和质量与工程师数量和水平相关,国内资深芯片设计工程师年薪一般在50-100万元之间。

另一方面,晶体管架构转向GAA,也在增加芯片成本。

当前随着深宽比不断拉高,FinFET逼近物理极限,为了制造出密度更高的芯片,环绕式栅极晶体管(GAAFET)成为新的技术选择。因此,晶体管结构从FinFET走向GAA,成为摩尔定律续命的关键。

- EDA成本

根据ESD Alliance数据显示,2020年EDA全球市场规模114.67亿美元,相对于几千亿美元的芯片市场来说占比较小,但EDA对芯片设计的效率和成本都起着至关重要的作用。

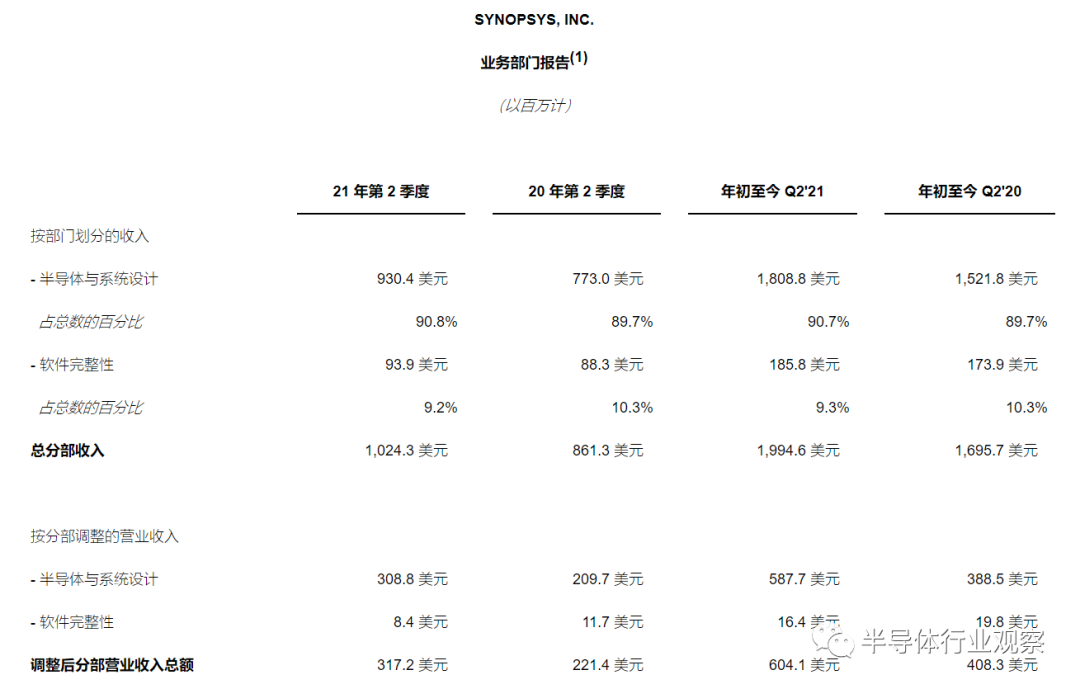

Synopsys 2021年Q2财报(图源:Synopsys)

Synopsys 2021年Q2财报(图源:Synopsys)根据Synopsys 最新财报来数据,2021年第二季度营收10.243亿美元,半导体和系统设计,包括EDA工具、IP产品、系统集成解决方案和相关服务;软件完整性,包括用于软件开发的安全和质量解决方案等。EDA营收达到5.876亿美元,占比在57%左右。

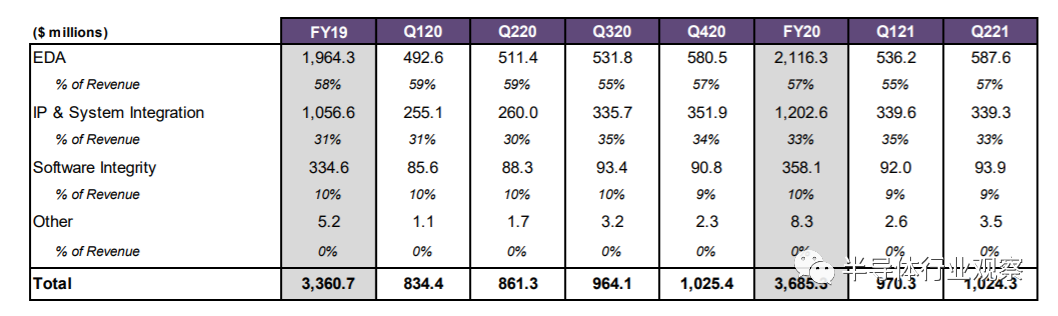

Synopsys财报数据(图源:Synopsys)

Synopsys财报数据(图源:Synopsys)据网上数据,20人的研发团队设计一款芯片所需要的EDA工具采购费用在100万美元/年(包括EDA和LPDDR等IP购买成本)。从EDA的行业属性及高昂的研发投入能够预测,待到3nm制程时,EDA工具授权费自然更是不菲。

- IP授权成本

半导体IP是指在集成电路设计中那些已验证、可复用、具有某种确定功能和自主知识产权功能的设计模块,芯片公司可以通过购买IP实现某个特定功能(例如ARM的Cortex系列CPU、Mali系列GPU IP授权等,其他小的模块也要购买,如音视频编****、DSP、NPU...等),这种类似“搭积木”的开发模式可大大缩短芯片的开发周期,在降低芯片设计难度的同时提高性能和可靠性。

2017-2020年Synopsys营收拆分(单位:百万美元)

2017-2020年Synopsys营收拆分(单位:百万美元)可见,IP作为技术含量最高的价值节点,随着芯片制程越来越先进,芯片价格的提升,IP研发难度和授权费用也将随之升高。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。