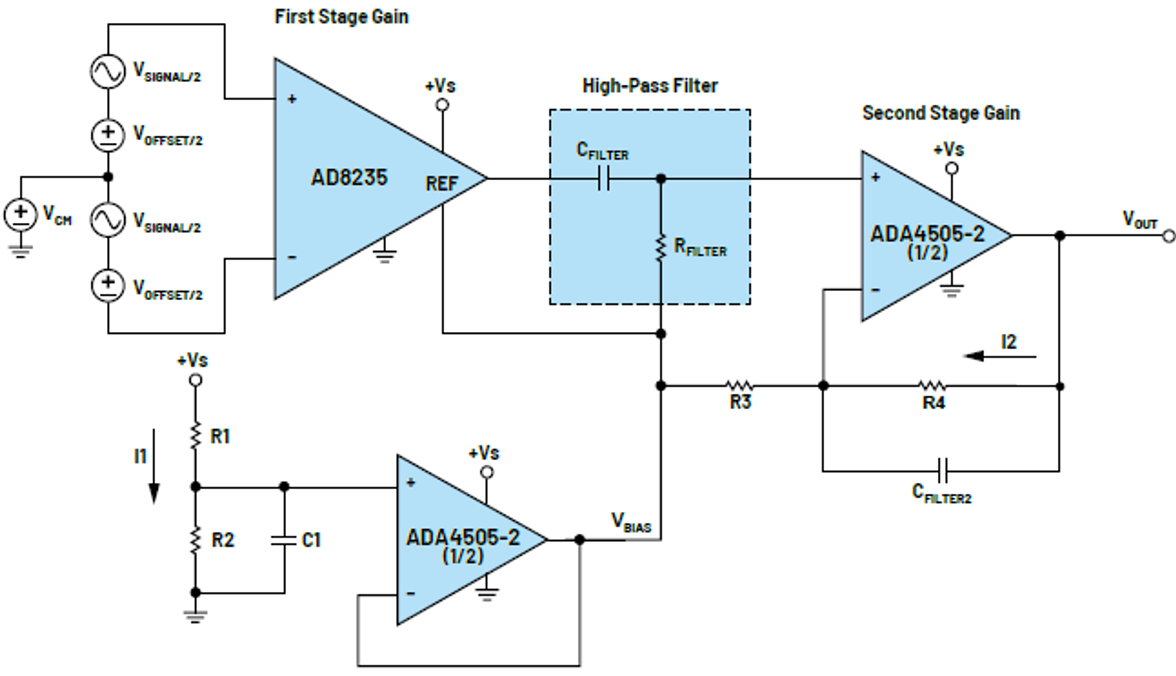

- 摘要本文将介绍低功耗系统在降低功耗的同时保持精度所涉及的时序因素和解决方案,以满足测量和监控应用的要求。文中将说明当所选ADC是逐次逼近寄存器(SAR) ADC时的时序影响因素。Σ-Δ架构的时序考虑因素有所不同(参见本系列文章的上篇)。本文探讨信号链在模拟前端时序、ADC时序和数字接口时序方面的考虑。 模拟前端时序考量图1中的三个模块可以分别予以考虑,从模拟前端(AFE)开始。信号链的类型会改变AFE,但有一些共同方面适用于大多数电路。图1.使用多路复用SAR ADC的AFE时序考量

- 关键字:

精密信号链 时序因素 ADI

时序因素介绍

您好,目前还没有人创建词条时序因素!

欢迎您创建该词条,阐述对时序因素的理解,并与今后在此搜索时序因素的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473