ip 文章 进入ip技术社区

IAR Embedded Secure IP保障产品开发后期安全性

- 凭借IAR的全新安全解决方案,嵌入式开发人员即使是在软件开发过程的后期阶段,也能轻松地为现有应用植入可靠的安全性,并直接投入生产瑞典乌普萨拉–2023年4月13日–嵌入式开发软件和服务的全球领导者IAR宣布推出IAR Embedded Secure IP解决方案,以帮助开发者即使在产品项目周期的后期,也能够为其固件应用植入嵌入式安全方案。通过IAR Embedded Secure IP解决方案,软件经理、工程师和项目经理可以在设计过程中的任何阶段,甚至是生产和制造阶段,以独特、灵活且安全的方式快速升级他们

- 关键字: IAR Embedded Secure IP 开发后期安全性

Codasip 宣布成立 Codasip 实验室,以加速行业前沿技术的开发和应用!

- 德国慕尼黑,2022年12月7日——处理器设计自动化和RISC-V处理器IP的领导者Codasip今日宣布成立Codasip实验室(Codasip Labs)。作为公司内部创新中心,新的Codasip实验室将支持关键应用领域中创新技术的开发和商业应用,覆盖了安全、功能安全(FuSa)和人工智能/机器学习(AI/ML)等方向。该实验室的使命在于识别和构建相关技术,以扩展定制计算的可能性,并加快具有定制化的、领域专用设计的差异化产品的开发,并缩短其上市时间。Codasip实验室将由公司创始人兼总裁马克仁(Ka

- 关键字: Codasip Codasip 实验室 IP RISC-V

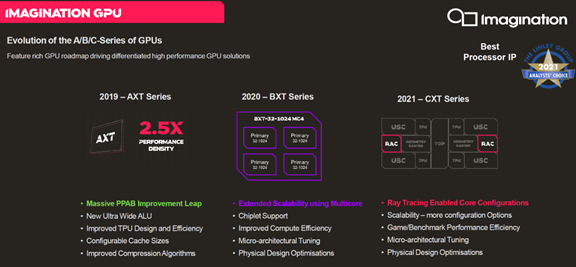

“倒金字塔”折射IP巨大价值,Imagination IP创新蝶变赋能半导体产业

- 过去50余年,芯片制程迭代沿着摩尔定律滚滚向前,并持续增强着芯片的算力与性能。现如今,无论是在SoC上集成越来越多的功能模块,又或是利用chiplet技术在先进制程下进一步提升芯片集成度,都充分展现了芯片性能、功耗和成本的改进不能仅仅依赖于制程的升级,而需从不同的维度拓展创新来延续摩尔定律的“经济效益”。这导致芯片设计变得越来越困难,IP的作用也愈加凸显,逐渐成为企业寻求设计差异化道路上的“秘钥”。 日前,在深圳举办的第10届EEVIA年度中国硬科技媒体论坛暨产业链研创趋势展望研讨会上,Imag

- 关键字: IP Imagination

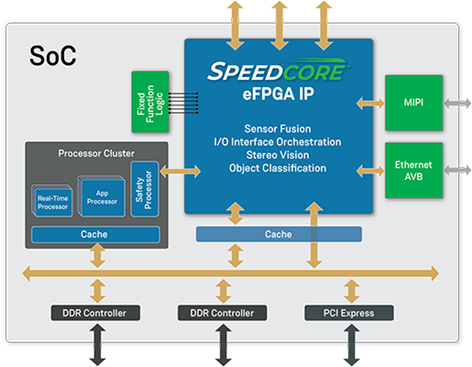

Imagination:SoC IP技术赋能未来硬核科技创新

- 在庞大的半导体细分产业链中,IP是其中最特殊的一环。正是借助众多的IP,才让半导体发展的步伐如此之快。IP是整个半导体上游产业链里面的核心,根据统计数据可以发现,每一元芯片能撑起200多元的社会经济,而每一元的IP,能支持20000元的社会经济价值,所以IP公司的存在是必要的。 随着芯片复杂度不断提升,特别是芯片进入SoC时代使得系统对各个环节技术要求越来越高,对一些中小型公司、创业公司来说,他们需要在成长过程中专注核心领域,没办法提供整个SoC完整的技术,所以它需要IP公司的支持,IP公司能协

- 关键字: Imagination SoC IP GPU

ip介绍

IP是英文Internet Protocol(网络之间互连的协议)的缩写,中文简称为“网协”,也就是为计算机网络相互连接进行通信而设计的协议。在因特网中,它是能使连接到网上的所有计算机网络实现相互通信的一套规则,规定了计算机在因特网上进行通信时应当遵守的规则。任何厂家生产的计算机系统,只要遵守 IP协议就可以与因特网互连互通。IP地址具有唯一性,根据用户性质的不同,可以分为5类。另外,IP还有进入 [ 查看详细 ]

热门主题

iPhone5S

IP(网络报文协议)

TCP/IP协议简介

IPC-6012

TCP/IP2.1

TCP/IP详解

IP-CORE

TCP/IP实现

http://211.157.110.170/Other/20070228/106.zip

TCP/IP协议栈

TCP/IP栈

TCP/IP网络通信控制器

TCP-IP-PPP协议栈

IPC-A-610C

IP协议

system-on-chip

TCP-IP协议栈

TCP-IP设备

TCP-IP

TCP-IP

Tcp_ip(Lwip)

Philips-Xilinx

~C/IP

IPC-810P

Script-Based

IP-STB

DAB-IP

TCP\IP

VO-IP

system-on-a-chip

IPC-6806

ICP/IP

IP-TV

CIP-51

FC-IP

Ti-chipcon

P2P-IPTV

EAP-SIP

UDP/IP

TCP\IP

TCP\IP

TCP\IP

树莓派

linux