- 单片机是一种可编程控制器,搭好硬件电路后,可以利用程序实现很多非常复杂的逻辑功能,与纯硬件电路相比,简化了硬件外围的设计、方便了逻辑的设计、丰富了逻辑的输出。不同厂家的单片机需要不同编程IDE来实现编程。在学习单片机之前,要先清楚单片机程序是如何烧写到单片机内部的,在烧写的过程中需要用到什么工具?因为不通用的烧写工具可能价格较贵,比如说Micorchip单片机使用的ICD系列编程器,单台价格在600-1000元人民币之间。今天和大学来认识一下单片机最常用的四种烧写方式和所使用到的工具。 1.使用JT

- 关键字:

JTAG SWD ISP SWIM

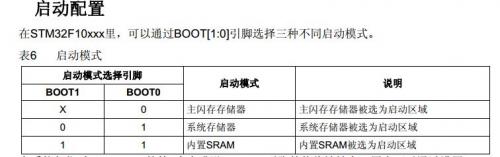

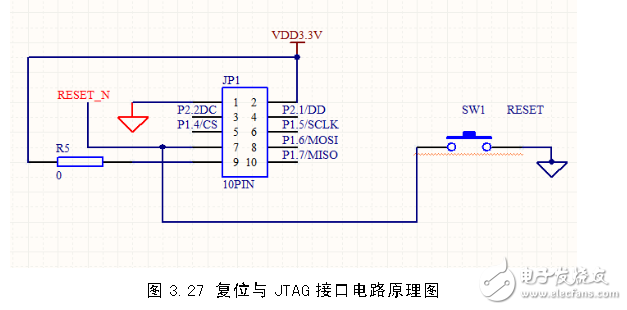

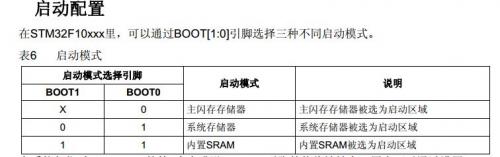

- STM32的基本系统主要涉及下面几个部分: 一、电源 1)、无论是否使用模拟部分和AD部分,MCU外围出去VCC和GND,VDDA、VSSA、Vref(如果封装有该引脚)都必需要连接,不可悬空; 2)、对于每组对应的VDD和GND都应至少放置一个104的陶瓷电容用于滤波,并接该电容应放置尽量靠近MCU; 3)、用万用表测试供电电压是否正确。调试时最好用数字电源供电,以便过压或过流烧坏板子。电压最好一步一步从进线端测试到芯片供电端。 二、复位、启动选择 1)、Boot引脚与JTAG无关。其仅是

- 关键字:

STM32 JTAG

- JTAG是一种标准的通讯口,用来传输调试信息。简单说它就是一种专用的串行通讯口,配合专用的设备(仿真器)与上位机进行通讯交换数据,在芯片内有专门的

- 关键字:

JTAG 嵌入式 ARM

- 通常所说的JTAG大致分两类,一类用于测试芯片的电气特性,检测芯片是否有问题;一类用于Debug。一般支持JTAG的CPU内都包含了这两个模块。 一个含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,Timers,GPIO等等的寄存器。 下面是一个设置AT91M40800的命令序列,关闭中断,设置CS0-CS3, 并进行

- 关键字:

JTAG CPU

- 通常所说的大致分两类,一类用于测试芯片的电气特性,检测芯片是否有问题;一类用于Debug;一般支持的CPU内都包含了这两个模块。 一个含有 Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,Timers,GPIO等等的寄存器。上面说的只是JTAG接口所具备的能力,要使用这些功能,还需要软件的配合,具体实现的功能则由具体的软件决定。例如下

- 关键字:

JTAG 嵌入式

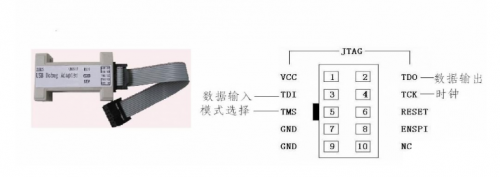

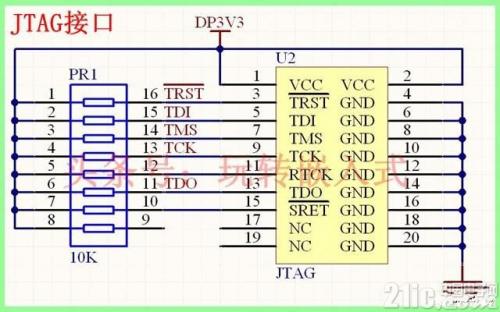

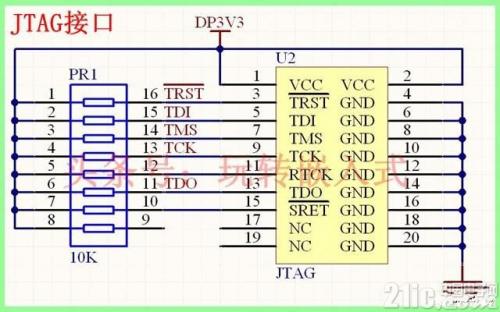

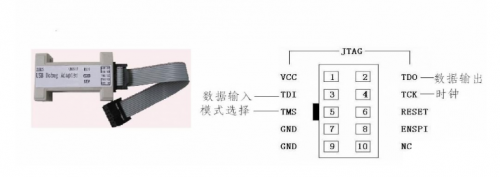

- JTAG(Joint Test AcTIon Group,联合测试行动组)是一种国际标准测试协议(IEEE 1149.1兼容)。标准的JTAG接口是4线——TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

JTAG是最基本的通讯协议之一,大家可以理解为与RX TX或者USB的道理是一样的,只是一种通讯手段,但与RX TX以及USB有很重大的不同,那就是这个JTAG协议是最底层的,说的通俗一点,一般来说,手机里边,CPU是老大,对吧?但在JTAG

- 关键字:

JTAG

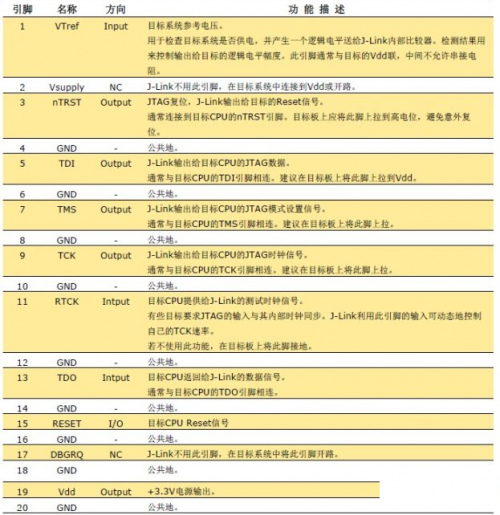

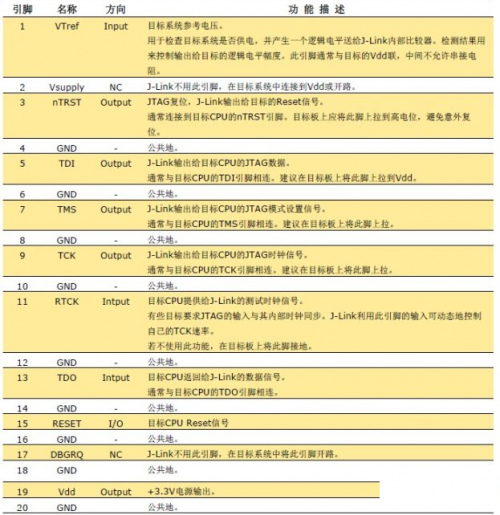

- JTAG各类接口针脚定义、含义

一、引脚定义

Test Clock Input (TCK) -----强制要求1

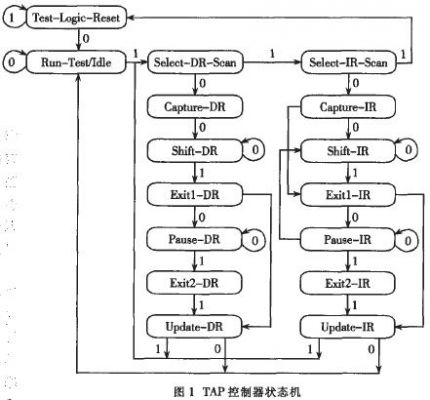

TCK在IEEE1149.1标准里是强制要求的。TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。

Test Mode SelecTIon Input (TMS) -----强制要求2

TMS信号在TCK的上升沿有效。TMS在IEEE1149.1标准里是强制要求的。TMS信号用来控制TAP状态机的转换。通过TM

- 关键字:

JLink JTAG

- 通常所说的JTAG大致分两类,一类用于测试芯片的电气特性,检测芯片是否有问题;一类用于Debug;一般支持JTAG的CPU内都包含了这两个模块。 一个含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,Timers,GPIO等等的寄存器。上面说的只是JTAG接口所具备的能力,要使用这些功能,还需要软件的配合,具体实

- 关键字:

JTAG 嵌入式

- 通常所说的大致分两类,一类用于测试芯片的电气特性,检测芯片是否有问题;一类用于Debug;一般支持的CPU内都包含了这两个模块。 一个含有 Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,Timers,GPIO等等的寄存器。上面说的只是JTAG接口所具备的能力,要使用这些功能,还需要软件的配合,具体实现的功能则由具体的软件决

- 关键字:

嵌入式 JTAG

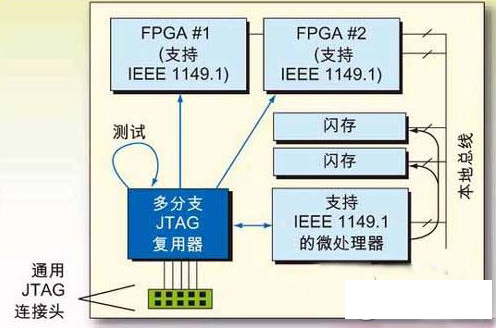

- 合理使用JTAG和IMPACT帮助你调试FPGA不能启动的问题-本来想着把GTX后面两篇博文找时间写了,但是最近实在是忙,一直在搭图像处理的AXI框架和整FPGA-DSP双平台的板子,下面先和大家分享一下调试心得。

- 关键字:

JTAG MPACT FPGA

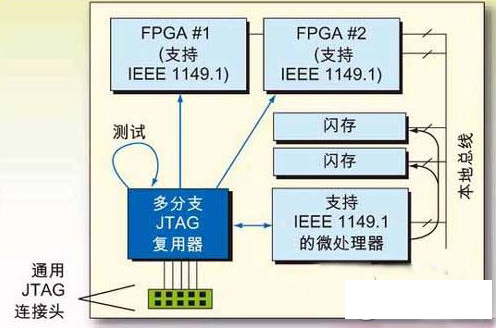

- FPGA实战开发技巧(9)-FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为CCLK) 由FPGA内部产生,且FPGA控制整个配置过程

- 关键字:

FPGA 赛灵思 JTAG

- 通常所说的JTAG大致分两类,一类用于测试芯片的电气特性,检测芯片是否有问题;一类用于Debug;一般支持JTAG的CPU内都包含了这两个模块。 一个含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,Timers,GPIO等等的寄存器。上面说的只是JTAG接口所具备的能力,要使用这些功能,还需要软件的配合,具体实

- 关键字:

嵌入式 JTAG

- 通常所说的JTAG大致分两类,一类用于测试芯片的电气特性,检测芯片是否有问题;一类用于Debug;一般支持JTAG的CPU内都包含了这两个模块。

一个含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,TImers,GPIO等等的寄存器。

上面说的只是JTAG接口所具备的能力,要使用这些功能,还需要软件的配合,具体

- 关键字:

JTAG 嵌入式

- 引言 IEEE 1149.1边界扫描测试标准(通常称为JTAG、1149.1或“dot 1”)是一种用来进行复杂IC与电路板上的特性测试的工业标准方法,大多数复杂电子系统都以这种或那种方式用到了IEEE1149.1(JTAG)标准。为了更好地理解这种方法,本文将探讨在不同年代的系统开发与设计中是如何使用JTAG的,通过借助过去有关JTAG接入的经验或投入,推动设计向新一代发展。 大多数复杂电子系统都以这种或那种方式用到了IEEE1149.1(JTAG)标准。如果系统采用的是复杂

- 关键字:

JTAG

jtag介绍

JTAG是英文“Joint Test Action Group(联合测试行为组织)”的词头字母的简写,该组织成立于1985 年,是由几家主要的电子制造商发起制订的PCB 和IC 测试标准。JTAG 建议于1990 年被IEEE 批准为IEEE1149.1-1990 测试访问端口和边界扫描结构标准。该标准规定了进行边界扫描所需要的硬件和软件。自从1990 年批准后,IEEE 分别于1993 年和 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473