这款测试芯片是业界首款采用12纳米FinFet(FF)技术为音频IP提供完整解决方案的产品。该芯片完美结合了高性能、低功耗和优化的占板面积,为电池供电应用提供卓越的音质与功能。这款专用测试芯片通过加快产品上市进程、提供同类最佳性能、及确保稳健的产品设计,坚定客户对Dolphin Design产品的信心,再度证实了Dolphin Design在混合信号IP领域的行业领先地位。2024年2月22日,法国格勒诺布尔——高性能模拟、混合信号、处理知识产权(IP)以及ASIC设计的行业领先供应商Dolphin De

关键字:

Dolphin Design 12纳米 12nm FinFet 成功流片

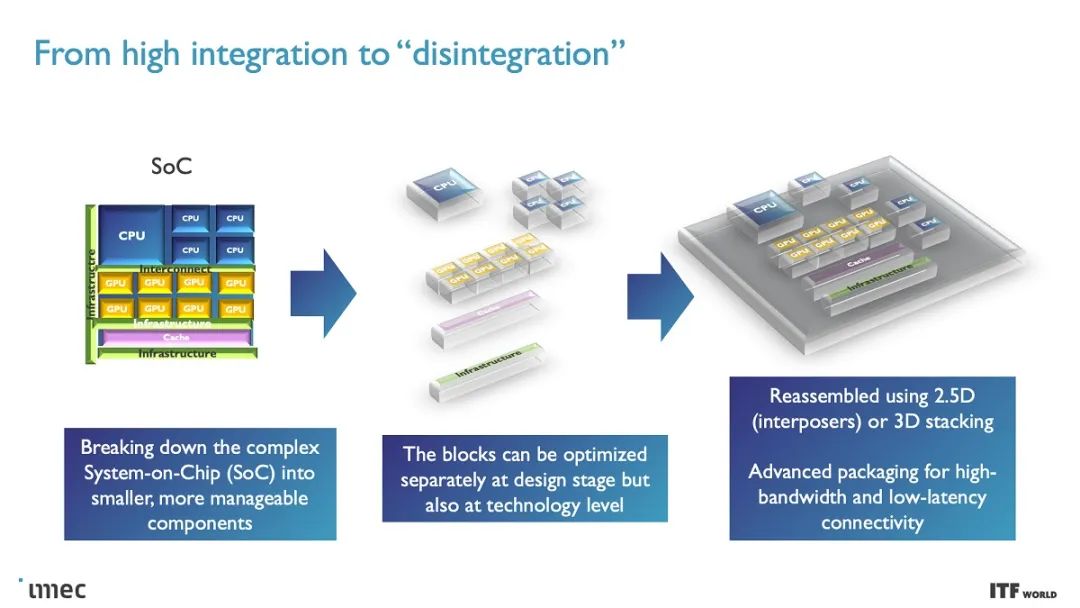

3D 芯片堆叠对于补充晶体管的发展路线图至关重要。

关键字:

FinFET

摘要:● 全新参考流程针对台积公司 N4PRF 工艺打造,提供开放、高效的射频设计解决方案。● 业界领先的电磁仿真工具将提升WiFi-7系统的性能和功耗效率。● 集成的设计流程提升了开发者的生产率,提高了仿真精度,并加快产品的上市时间。近日宣布,携手是德科技(Keysight)、Ansys共同推出面向台积公司业界领先N4PRF工艺(4纳米射频FinFET工艺)的全新参考流程。该参考流程基于新思科技的定制设计系列产品,为追求更高预测精度

关键字:

新思科技 是德科技 Ansys 台积公司 4 纳米 射频 FinFET 射频芯片设计

● 新参考流程采用台积电 N4PRF 制程,提供了开放、高效的射频设计解决方案● 强大的电磁仿真工具可提升 WiFi-7 系统的性能和功率效率● 综合流程可提高设计效率,实现更准确的仿真,从而更快将产品推向市场是德科技、新思科技和Ansys携手为台积电的先进4nm射频FinFET制程打造全新参考流程,助力RFIC半导体设计加速发展是德科技、新思科技公司和 Ansys 公司近日宣布携手推出面向台积电 N4PRF 制程的新参考流程。N4P

关键字:

是德科技 新思科技 Ansys 台积电 4nm射频 FinFET

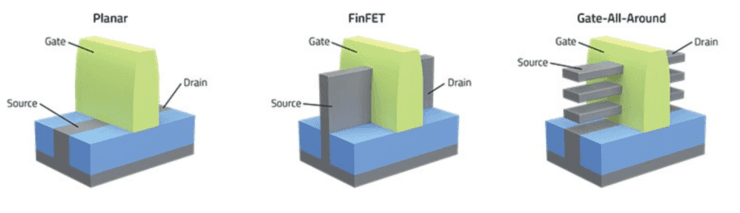

近日,比利时微电子研究中心(IMEC)发表1纳米以下制程蓝图,分享对应晶体管架构研究和开发计划。外媒报导,IMEC制程蓝图显示,FinFET晶体管将于3纳米到达尽头,然后过渡到Gate All Around(GAA)技术,预计2024年进入量产,之后还有FSFET和CFET等技术。△Source:IMEC随着时间发展,转移到更小的制程节点会越来越贵,原有的单芯片设计方案让位给小芯片(Chiplet)设计。IMEC的制程发展愿景,包括芯片分解至更小,将缓存和存储器分成不同的晶体管单元,然后以3D排列堆叠至其

关键字:

IMEC 1nm 制程 FinFET

● 恩智浦和台积电联合开发采用台积电16纳米FinFET技术的嵌入式MRAM IP● 借助MRAM,汽车厂商可以更高效地推出新功能,加速OTA升级,消除量产瓶颈● 恩智浦计划于2025年初推出采用该技术的新一代S32区域处理器和通用汽车MCU首批样品 荷兰埃因霍温——2023年5月22日——恩智浦半导体(NXP Semiconductors N.V.,纳斯达克股票代码:NXPI)近日宣布与台积电合作交付行业首创的采用16纳米

关键字:

恩智浦 台积电 FinFET 嵌入式MRAM

意法半导体(ST)和GlobalFoundries (GF)刚刚签署了一份谅解备忘录,将在意法半导体位于法国Crolles的现有晶圆厂旁边新建一座联合运营的300毫米半导体晶圆厂。新工厂将支持多种半导体技术和工艺节点,包括FD-SOI。ST和GF预计,该晶圆厂将于2024年开始生产芯片,到2026年将达到满负荷生产,每年生产多达62万片300毫米晶圆。法国东南部的Crolles,距离意大利边境不远,长期以来一直是FD-SOI发展的温床。从许多方面来看,FD-SOI是一种技术含量较低的方法,可以实现FinF

关键字:

FD-SOI GAAFET FinFET

英特尔近期于美国檀香山举行的年度VLSI国际研讨会,公布Intel 4制程的技术细节。相较于Intel 7,Intel 4于相同功耗提升20%以上的效能,高效能组件库(library cell)的密度则是2倍,同时达成两项关键目标:它满足开发中产品的需求,包括PC客户端的Meteor Lake,并推进先进技术和制程模块。 英特尔公布Intel 4制程的技术细节。对于英特尔的4年之路,Intel 4是如何达成这些效能数据? Intel 4于鳍片间距、接点间距以及低层金属间距等关键尺寸(Critic

关键字:

Intel 4 制程技术 FinFET Meteor Lake

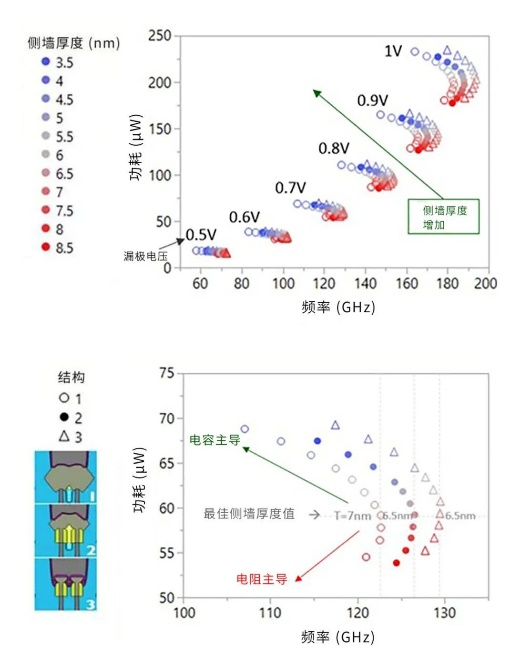

虽然栅极间距(GP)和鳍片间距(FP)的微缩持续为FinFET平台带来更高的性能和更低的功耗,但在5nm及更先进节点上,兼顾寄生电容电阻的控制和实现更高的晶体管性能变得更具挑战。泛林集团在与比利时微电子研究中心 (imec) 的合作中,使用了SEMulator3D®虚拟制造技术来探索端到端的解决方案,运用电路模拟更好地了解工艺变化的影响。我们首次开发了一种将SEMulator3D与BSIM紧凑型模型相耦合的方法,以评估工艺变化对电路性能的影响。这项研究的目的是优化先进节点FinFET设计的源漏尺寸和侧墙厚

关键字:

泛林 5nm FinFET

观察2021年主导半导体产业的新技术趋势,可以从新的半导体技术来着眼。基本上半导体技术可以分为三大类,第一类是独立电子、计算机和通讯技术,基础技术是CMOS FinFET。在今天,最先进的是5奈米生产制程,其中有些是FinFET 架构的变体。这是大规模导入极紫外光刻技术,逐步取代多重图形光刻方法。 图一 : 半导体的创新必须能转化为成本可承受的产品。我们知道,目前三星、台积电和英特尔等主要厂商与IBM 合作,正在开发下一代3/2奈米,在那里我们会看到一种新的突破,因为他们最有可能转向奈米片全环绕

关键字:

CMOS FinFET ST

中芯国际联席CEO赵海军透露了公司的先进工艺的情况,表示FinFET工艺已经达产,每月1.5万片,客户不断进来。在最近的财报电话会上,中芯国际联席CEO赵海军透露了公司的先进工艺的情况,表示“我们的FinFET工艺已经达产,每月1.5万片,客户多样化,不同的产品平台都导入了。(这部分)产能处于紧俏状态,客户不断进来。”根据之前的报道,中芯国际的FinFET工艺有多种类型,其中第一代FinFET工艺是14nm及改进型的12nm,目前1.5万片产能的主要就是14/12nm工艺,第二代则是n+1、n+2工艺,已

关键字:

中芯国际 FinFET

要点: 用于GF 12LP+解决方案的DesignWare IP核产品组合包括USB4、PCIe 5.0、Die-to-Die HBI和112G USR/XSR、112G Ethernet、DDR5、LPDDR5、MIPI、OTP NVM等 两家公司之间的长期合作已成功实现了DesignWare IP核从180纳米到12纳米的开发,可应用于广泛领域新思科技(Synopsys, Inc.,纳斯达克股票代码:SNPS)今日宣布与GLOBALFOUNDRIES®(GF®)开展合作,开发用于G

关键字:

新思科技 12LP+FinFET DesignWare IP

半导体代工厂格罗方德(GLOBALFOUNDRIES)宣布,旗下最先进的FinFET解决方案「12LP+」已通过技术验证,目前准备投入生产。 格罗方德的差异化「12LP+」解决方案主要针对AI训练以及推论应用进行优化。本解决方案建立于验证过的平台上,具有强大的制造生态系统,可为芯片设计师带来高效能的开发体验,及快速的上市时间。 为达到性能、功耗和面积的组合,12LP+导入了若干新功能,包含更新后的标准组件库、用于2.5D封装的中介板,与一个低功耗的0.5V Vmin SRAM记忆单元,以支持AI处理器与内

关键字:

格罗方德 12LP+ FinFET AI

finfet介绍

FinFET称为鳍式场效晶体管(FinField-effecttransistor;FinFET)是一种新的互补式金氧半导体(CMOS)晶体管,闸长已可小于25奈米,未来预期可以进一步缩小至9奈米,约是人类头发宽度的1万分之1。由于此一半导体技术上的突破,未来芯片设计人员可望能够将超级计算机设计成只有指甲般大小。 FinFET源自于目前传统标准的晶体管—场效晶体管 (Field-ef [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473