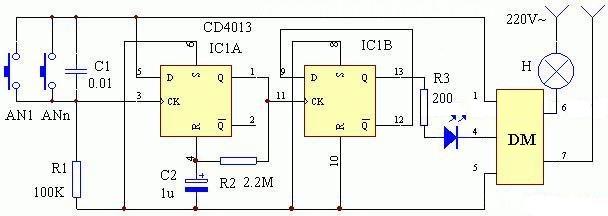

- 实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握D触发器原理;(3)学习用Verilog HDL语言行为机描述方法描述D触发器电路。实验任务本实验的任务是描述一个带有边沿触发的同步D触发器电路,并通过STEP FPGA开发板的12MHz晶振作为触发器时钟信号clk,拨码开关的状态作为触发器输入信号d,触发器的输出信号q和~q,用来分别驱动开发板上的LED,在clk上升沿的驱动下,当拨码开关状态变化时LED状态发生相应变化。实验原理从D触发器的特

- 关键字:

D触发器 FPGA Lattice Diamond Verilog HDL

- 我们的设计需要多大容量的芯片?我们的设计能跑多快?这是经常困扰工程师的两个问题。对于前一个问题,我们可能还能先以一个比较大的芯片实现原型,待原型完成再选用大小合适的芯片实现。对于后者,我们需要一个比较精确的预估。

- 关键字:

频率计算 D触发器 FPGA Tlogic

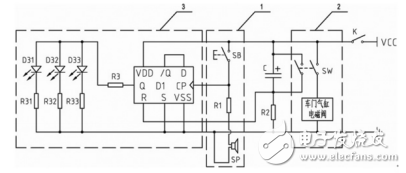

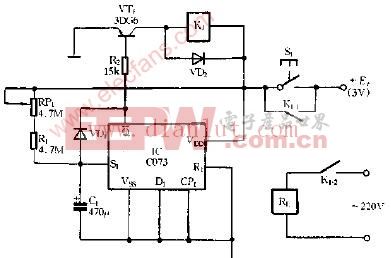

- 图中所示是用CMOS电路D触发器组成的触摸式反转开关。图中在CL端与触摸点K之间加入了一个或非门组成的单稳态触发器,它将手指触摸时送进来的电压,展宽成一个固定宽度...

- 关键字:

D触发器 组成触摸式 反转开关

- 从D触发器的真值表可知,当时钟脉冲CL=1时,数据输入端D的状态会被“置放”入触发器中去,而与触发器原状无关。如果当时钟冲CL=1,D端状态不旋转放入触发器中...

- 关键字:

D触发器 信号电路图

- //基本D触发器 module D_EF(Q,D,CLK) input D,CLK; output Q; reg Q; //在always语句中被赋值的信号要声明为reg类型 寄存器定义 always @ (posedge CLK) //上升沿,下降沿用negedge表示,^_^ 需要记忆 begin Q <= D; end endm

- 关键字:

D触发器 Verilog

- 导读:触发器又称为双稳态多谐振荡器,是一种可以存储电路状态的电子元件,广泛用于运算器、计算器、存储器中。最简单的触发器便是RS触发器了,相信大家都有所了解,今天在此基础上,我们一起来八一八D触发器原理的真相。

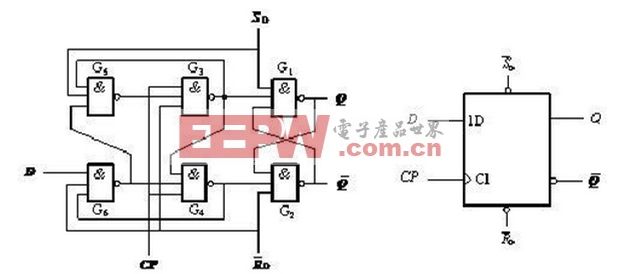

一、D触发器原理- -简介

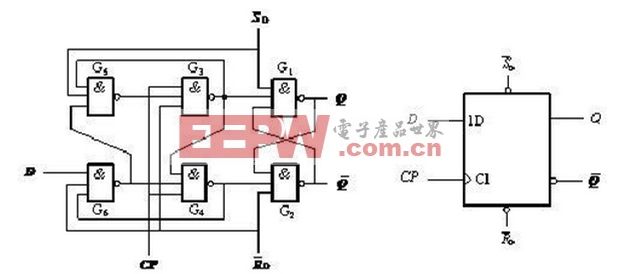

D触发器(data flip-flop)也称为维持-阻塞边沿D触发器,由六个与非门组成,其电路图及其逻辑符号如下图所示。其中G1和G2构成基本的RS触发器,G3和G4构成时钟控制电路,G5和G6组成数据输入电路。由于 分别为复位端和置位端,在分析D触发器工作原

- 关键字:

D触发器 D触发器原理

- 入门前

刚才开始接触逻辑设计很多人会觉得很简单:因为verilog的语法不多,半天就可以把书看完了。但是很快许多人就发现这个想法是错误的,他们经常埋怨综合器怎么和自己的想法差别这么大:它竟然连用for循环写的一个计数器都不认识!

相信上一段的经历大部分人都曾有,原因是做逻辑设计的思维和做软件的很不相同,我们需要从电路的角度去考虑问题。

在这个过程中首先要明白的是软件设计和逻辑设计的不同,并理解什么是硬件意识。

软件代码的执行是一个顺序的过程,编绎以后的机器码放在存储器里,等着C

- 关键字:

逻辑设计 verilog D触发器

d触发器介绍

边沿D 触发器:

负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

[

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473