- 提出了在FPGA上实现H.264中整数变换量化的方法,设计了基于动态数据宽度和流水线技术的软核(IP),在处理速度和硬件资源方面分别进行优化。此软核作为PowerPC的一个硬件加速模块在Xilinx Virtex-ⅡPRO中进行了验证。

- 关键字:

动态数据宽度 流水线 软核

- 在爆炸场压力测试中,冲击波超压峰值随着弹药的当量和到爆心距离的变化十分显著。传统测试系统的测试参数难以更改,灵活性差,往往需要重新设计电路以满足不同测试要求。为了提高测试系统的灵活性及电路复用性,设计了基于可配置FPGA软核的测试系统。通过调用并修改可移植软核,以实现系统的快速设计,通过灵活设置测试参数完成不同测试任务。对系统准确性进行了验证,应用到静爆试验中,有效获得了压力数据。

- 关键字:

FPGA 软核 冲击波 存储测试

- 众多FPGA 应用均可通过使用简单的软核处理器来简化时序控制结构的生成,从而深受其益。作者:Adam P. Taylore2v公司工程系统负责人aptaylor@theiet.orgPicoBlaze 是一款结构紧凑的8 位软核微控制器,FPGA工程师可在

- 关键字:

PicoBlaze 软核

- 基于Nios II 软核处理器的SD卡接口设计(二),接上文基于Nios II 软核处理器的SD卡接口设计(一) 2.1 SD卡初始化在对SD 卡进行读/写之前,必须知道卡的类型、卡的容量、卡的大小等信息。具体来说,初始化函数主要完成以下工作:(1) 微处理器(这里指Nios II)复位

- 关键字:

SD 接口 设计 处理器 软核 Nios II 基于

- 基于Nios II 软核处理器的SD卡接口设计(一), 摘要:随着FPGA的低成本化和整合资源的不断增强,FPGA在整个嵌入式市场中的份额在不断增加。基于FPGA的NiosII软核以其高度的设计灵活性和完全可定制性在现今电子产品设计及工业控制中扮演着重要的角色。此外,以SD卡

- 关键字:

SD 接口 设计 处理器 软核 Nios II 基于

- 引言PicoBlaze是Xilinx公司为Virtex、Spartan系列FPGA和CoolRunnerII系列CPLD设计的8位嵌入式处理器软核。PicoBlaze嵌入式处理器具有高达44~100 MIPS的指令执行速度,并具有效率高、占用资源少等优点,可以方便地嵌

- 关键字:

PicoBlaze 软核 仿真 调试

- 从IP核的提供方式上,通常将其分为软核、固核和硬核这3类。从完成IP核所花费的成本来讲,硬核代价最大;从使用灵活性来讲,软核的可复用使用性最高。1. 软核(Soft IP Core)软核在EDA 设计领域指的是综合之前的寄存器传

- 关键字:

FPGA 软核 概念 分析

- 摘要:NiosII软核处理器是Altera公司开发,基于FPGA操作平台使用的一款高速处理器,为了适应高速运动图像采集,提出...

- 关键字:

SOPC 步进电机 硬件描述语言 软核

- 摘要:NiosII软核处理器是Altera公司开发,基于FPGA操作平台使用的一款高速处理器,为了适应高速运动图像采集,提出了一种基于NiosII软核处理的步进电机接口设计,使用verilog HDL语言完成该接口设计,最后通过Ouart

- 关键字:

电机 接口 设计 步进 处理器 NiosII 软核 基于

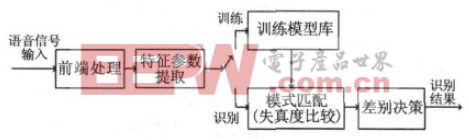

- 引言人脸检测跟踪是计算机视觉中十分重要的研究领域,正受到越来越多的关注。传统基于PC平台的人脸检测跟踪系统体积大,不能满足便携的要求,更不适合露天使用;而采用通用的DSP芯片组成的系统,外围电路较复杂,设计

- 关键字:

Nios 软核 人脸检测 系统设计

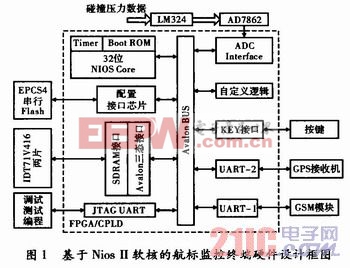

- 摘要 阐述了基于NiosⅡ软核的内河航标监控系统的设计方法,及AD7862控制电路的VHDL设计。从系统的角度提出航标监控系统的完整设计方案,给出基于Nios II的航标监控终端硬件设计框图,并得到在Modesim中进行仿真的结果

- 关键字:

航标 监控系统 设计 内河 软核 Nios II 基于

- 为解决不同性能指标数据采集系统开发时间较长的问题,提出了一种将FPGA软核技术应用于高速数据采集系统设计的方法。系统以Xilinx公司的FPGA为例设计软核,使用VHDL语言对软核进行模块化设计。介绍了数据采集系统的硬件电路、USB固件程序、USB驱动程序以及LabVIEW上位机的设计。该数据采集系统结构可移植性强,有利于缩短同类型系统设计研发周期。

- 关键字:

FPGA 软核 高速数据 采集

- 摘要:门光子计数器是量子光学实验中单光子探测常用的数据采集设备,用于收集单光子探测器探测到的单个光子信号。由于不同的场合需要用到不同的计数模式,商用的计数器往往难以满足具体的需求,或者造成采集效率低下

- 关键字:

Microblaze FSL 软核 门光子

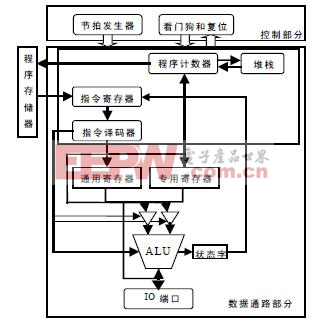

- 8位RISC MCU IP软核仿真的新方法, 本文提出的建立虚拟指令存储器模块对MCU IP核仿真的方案和自动生成指令测试文件的方法,大大提高了MCU IP核仿真和验证的效率。此方法不仅对本文中MCU IP核的仿真和验证有效,也可用于同类中其它IP核的仿真和验证。例如当对MCU进行升级设计、扩展寻址范围或指令宽度时,只要修改仿真文件和转化程序的相关参数即可。

- 关键字:

真的 方法 软核 IP RISC MCU 8位

- 摘要:与通常采用外围的CPLD器件和CPU来产生配置接口控制逻辑的方法不同,本文设计了采用嵌入到FPGA的Leon3开源CPU软核来控制实现Virtex系列FPGA的SelectMap接口配置的方法,可将其应用于对FPGA芯片的在线配置。该方

- 关键字:

SelectMap Leon3 FPGA 软核

软核介绍

前不久,Altera 正式推出了Nios II系列32位RSIC嵌入式处理器。Nios II系列软核处理器是Altera的第二代FPGA嵌入式处理器,其性能超过200DMIPS,在Altera FPGA中实现仅需35美分。Altera的Stratix 、Stratix GX、 Stratix II和 Cyclone系列FPGA全面支持Nios II处理器,以后推出的FPGA器件也将支持Nios I [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473