- IT之家 9 月 19 日消息,综合外媒 9To5Mac 和 Apple Insider 报道,有部分苹果 iPhone 14 Pro 用户称,第三方 App 使用相机时出现了画面模糊和抖动问题,同时伴随着物理的嗡嗡声。用户报告称,Snapchat、TikTok 和 Instagram 等流行的第三方 App 都出现了该问题,且似乎是和 OIS 光学防抖有关。从下面的视频可以看到这一问题,似乎是由于光学防抖与第三方 App 不兼容,导致镜头自己乱晃,并发出奇怪的声音。IT之家了解到,该问题目前仅限 iPh

- 关键字:

苹果 iPhone 14 Pro 相机 App 模糊 抖动

- ADC是现代数字解调器和软件无线电接收机中连接模拟信号处理部分和数字信号处理部分的桥梁,其性能在很大程度上决定了接收机的整体性能。在A/D转换过程

- 关键字:

ADC 抖动 采样时钟 电路设计

- 如何选择环路带宽平衡抖动、相位噪声、锁定时间或杂散-作为最重要的设计参数之一,选择环路带宽涉及到抖动、相位噪声、锁定时间或杂散之间的平衡。适合抖动的最优环路带宽BWJIT也是数据转换器时钟等许多时钟应用的最佳选择。如果BWJIT并非最佳选择,首先要做的仍是寻找最优环路带宽。

- 关键字:

环路带宽 抖动 相位噪声 锁定时间

- 在嵌入式计算机系统中,键盘是最基本的人机交互输入设备。除了使用通用的标准键盘外,实际工程应用中更需要进行单独设计并购程专用的各种小键盘。随着EDA(电子设计自动化)技术的迅速发展,利用FPGA来实现各种数字电路将是非常经济和便利的。文中介绍键盘扫描模块地实现原理,阐迷了一种基于FPGA的键盘扫描模块的实现方法。

- 关键字:

健盘扫描 嵌入式系统 抖动 FPGA EDA

- 抖动测量一直被称为示波器测试测量的最高境界。传统最直观的抖动测量方法是利用余辉来查看波形的变化。后来演变为高等数学概率统计上的艰深问题,抖动测量结果准还是不准的问题就于是变得更加复杂。时钟的特性可以用

- 关键字:

抖动 相噪 测量

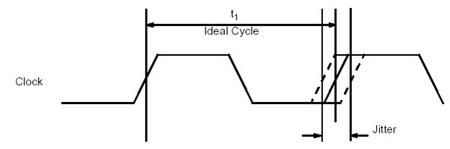

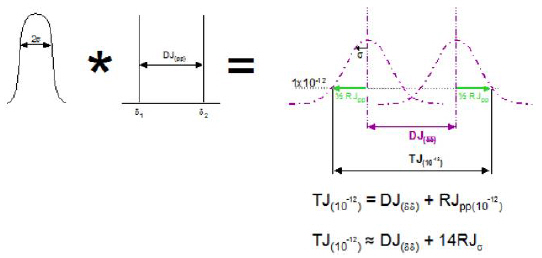

- 随着高速应用中的定时要求日趋严格,对各种抖动技术规范的更深入理解现已变得非常重要。从 10Gb 以太网网络到 PCIe 等高速互联技术,链路中所暗含的稳健性都与降低定时裕度密切相关。简言之,抖动就是信号边沿与理

- 关键字:

抖动 定时 相位噪声 时间间隔误差

- 十几年前,频率控制行业推出了基于锁相环(PLL)的振荡器,这是一项开拓性创新技术,采用了传统晶体振荡器(XO)所没有的多项特性。凭借内部时钟合成器IC技术,基于PLL的XO可编程来支持更宽广的频率范围。这一突破消除了

- 关键字:

锁相环 PLL 振荡器 抖动 相位噪声

- 了解时钟信号的数字定时以及诸如抖动、漂移、上升时间、下降时间、稳定时间、迟滞和眼图等常用术语。 本教程是仪器基础教程系列的一部分。

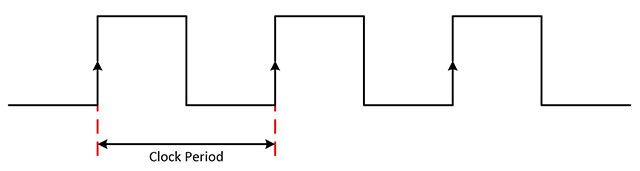

1. 时钟信号

发送数字信号其实发送的就是一串由0或1组成的数字序列。 然而,与不同设备进行通信时,定时信息要与发送的位相关联。 数字波形作为时钟信号的参考。 您可以将时钟信号看成是一个指挥者,它为数字电路系统的各个部分提供定时信号,使每个过程都可在精确的时间点触发。

时钟信号是具有固定周期的方波。 周期是指一个时钟边沿到下一个同类时钟边沿之间的时间间隔

- 关键字:

时钟 抖动

- 为什么抖动很重要? 在当今数据通信、有线及无线基础设施以及其它高速应用等高级系统中,时钟抖动是整体系统性能的关键因素。要达到所需的系统抖动性能,一定要保持尽可能低的时钟抖动,并在整个分配网络上分配低抖动时钟源。 随着系统要求的不断提升,问题也随之而来:时钟线路上添加的简单缓冲器会不会让时钟抖动变得更差?如果会,在添加简单缓冲器之前应该考虑什么问题? 图1:系统级说明 附加抖动定义 这就是存在附加抖动的地方。附加抖动可定义为器件本身为输入信号增加的抖动数量。它的计算公式为,假设噪声过程是随机的,

- 关键字:

定时 抖动

- 简介:本文介绍了抖动和相位噪声的基础知识,以及它的引发因素、和观察分析的探讨。

抖动(Jitter)反映的是数字信号偏离其理想位置的时间偏差。高频数字信号的bit周期都非常短,一般在几百ps甚至几十ps,很小的抖动都会造成信号采样位置电平的变化,所以高频数字信号对于抖动都有严格的要求。

实际信号的很复杂,可能既有随机抖动成分(RJ),也有不同频率的确定性抖动成分(DJ)。确定性抖动可能由于码间干扰或一些周期性干扰引起,而随机抖动很大一部分来源于信号上的噪声。下图

- 关键字:

射频 抖动

- 抖动测量一直被称为示波器测试测量的最高境界。传统最直观的抖动测量方法是利用余辉来查看波形的变化。后来演变为高等数学概率统计上的艰深问题,抖动测量结果准还是不准的问题就于是变得更加复杂。时钟的特性可以用频率计测量频率的稳定度,用频谱仪测量相噪,用示波器测量TIE抖动、周期抖动、cycle-cycle抖动。

- 关键字:

时钟 抖动 相噪 测量 频谱仪 示波器

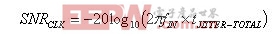

- 您在使用一个高速模数转换器 (ADC) 时,总是期望性能能够达到产品说明书载明的信噪比 (SNR) 值,这是很正常的事情。您在测试 ADC 的 SNR 时,您可能会连接一个低抖动时钟器件到转换器的时钟输入引脚,并施加一个适度

- 关键字:

详解 SNR 抖动

- 摘要在选择时钟器件时,抖动指标是最重要的关键参数之一。但不同的时钟器件,对抖动的描述不尽相同,如不带锁相环的时钟驱动器有附加抖动指标要求,而带锁相环实现零延时的时钟驱动器则有周期抖动和周期间抖动指。同

- 关键字:

时钟器件 抖动 性能

- 引 言在电子设计和测量过程中,信号边沿抖动是我们经常碰到的现象。如下图示,t1,t2,...,t4,信号电平变化时出现多次随机快速变化,这种随机变化在有的场合可以容忍,但大部分时候是难以容忍的,比如精密测量、精

- 关键字:

CPLD 宽带 抖动

- 让我们来对一个具有 400 fs 抖动时钟电路和 ~73 dB 热噪声的 14 位 ADC 进行分析。低输入频率(例如:10MHz 等 ...

- 关键字:

时域时钟 抖动

抖动介绍

英文叫做dithering.

抖动的定义是“数字信号的各个有效瞬时对其当时的理想位置的短期性偏离”,这意味着抖动是不希望有的数字信号的相位调制。相位偏离的频率称为抖动频率,与抖动有密切关系的第二个参数称为漂移,把它定义为“数字信号的各个有效瞬间相对其当时的理想位置的长期偏离”。到目前为止,在抖动和漂移之间的界限还没有明确的定义,通常具有频率低于1Hz至10Hz相位变化部分称为漂移。由于信 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473