高性能时钟产品趋势漫谈

4.FPGA或ASIC中的应用

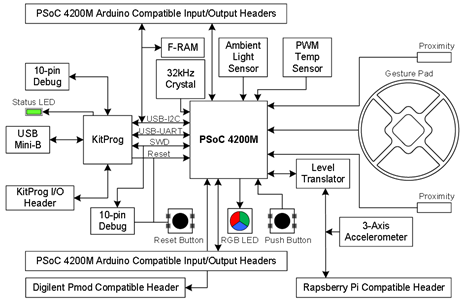

本文引用地址:http://www.amcfsurvey.com/article/97854.htmCypress的 Sudhir 介绍说,可编程时钟诸如FleXO系列可生成无标准频率,从而优化FPGA或ASIC的性能。在实际调试过程中,频率适当地提快或放慢一点儿,都会对整个系统的性能有很大的提高。尤其是在通信设备里,一个6U甚至更大的机箱,时钟信号需要经过不同的板卡,因此会产生时钟信号的延迟,即时延。因此,在不同PCB(印制电路板)上传输时时钟是易变的。但信号是需要同步的,尽管不同板之间的信号时延是设计者难以控制的。有了可编程时钟器件,设计者就可以在系统联调时做一些微调,这样就把原来需要用的一些其他方式(比如每过一个板子,后面的信号都要去进行一次同步)省掉了,使眼图和误码率最终满足要求。

时钟供应商的竞争优势

Maxim:拥有自己的晶圆厂和安装、测试工厂,并在近期开发出了新的高速集成工艺和高精度仿真模块。

凌力尔特:器件具有简单、紧凑、低功率和坚固的特点,并为晶体或陶瓷谐振器提供了一种真正的替代方案。

安森美:所有的产品都使用从输入到输出方面完全差异化的设计。例如,NBXxxxx高性能单频和双频PureEdge 时钟模块系列非常适合高速网络、电信和高端计算等应用。

ADI:专注于数据转换器时钟。在整数和分数N分频锁相环技术方面均已拥有强大的专业技术,加上领先的DDS技术,被用于数字锁相环频率合成解决方案。

IDT:时钟产品是IDT的战略重点,而不是一个辅助产品线。IDT并不提供现成的解决方案,而是与客户紧密合作,创建针对其系统的良好解决方案。

Sitime:1)通过采用Frac-N PLL分数分频锁相环路技术,可最大程度也实现频率定制编程。2)采用了基于MEMS(微机电系统)技术的解决方案。

Silicon Labs:高性能时钟为下一代多速率线路卡提供了一个高度集成的、具有成本效益的抖动衰减的解决方案,支持大量的客户端和线路方面的接口。(注:关于此次报道更多详情,请访问本刊网站近期推出的同名专题。)

参考文献

[1]王莹.时钟发生器的性能趋势[R/OL].http://wangying1.spaces.eepw.com.cn/articles/article/item/58546

[2]Johnson J.高清世界时钟所面临的挑战(上)[J].电子产品世界,2007(12):106-109

[3]Johnson J.高清世界时钟所面临的挑战(下)[J].电子产品世界,2008(1):98-102

[4]Numm P.如何产生数据采集系统的参考时钟[J].电子产品世界,2006(4上半月):105-107

[5]Halfhill T R.ARM能取消时钟吗[J].电子产品世界,2006(5上半月):60-64

评论