GLOBALFOUNDRIES介绍22纳米及更小尺寸技术

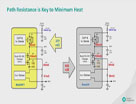

GLOBALFOUNDRIES日前介绍了一种创新技术,该技术可以克服推进高 k金属栅(HKMG)晶体管的一个主要障碍,从而将该行业向具有更强计算能力和大大延长的电池使用寿命的下一代移动设备推进了一步。

本文引用地址:http://www.amcfsurvey.com/article/95394.htm众所周知,半导体行业一直致力于克服似乎难以逾越的困难,以延续更小、更快、更节能的产品趋势。研究是通过GLOBALFOUNDRIES参与IBM技术联盟来与IBM合作的形式进行的,旨在继续将半导体元件的尺寸缩小到22纳米节点及更小尺寸。

在2009年于日本京都举行的VLSI技术研讨会上,GLOBALFOUNDRIES首次展示了可使高k金属栅(HKMG)晶体管的等效氧化层厚度(EOT)缩小到远远小于22纳米节点所需水平,同时保持了低漏电、低阈值电压和优越的载流子迁移率等优点的技术。

GLOBALFOUNDRIES技术与研发高级副总裁Gregg Bartlett说:“HKMG是GLOBALFOUNDRIES技术路线图的关键组成部分。这种进展可能最终为客户提供另一种提高其产品性能的工具,尤其是在快速增长的具有长电池寿命的超便携笔记本电脑和智能手机市场。通过与IBM及联盟伙伴的合作,我们利用我们的全球知识库开发先进的技术,帮助我们的客户处于半导体制造的前沿。”

为了保持HKMG晶体管的开关精度,必须减少高k氧化层的等效氧化层厚度。然而,减少EOT会增加泄漏电流,从而增加微芯片的功耗。GLOBALFOUNDRIES和IBM已经开发出一种可克服这一障碍的新技术,首次展示了将EOT缩小到远远低于22纳米节点,同时保持所需的漏电流、阈值电压和载流子迁移率是可以实现的。通过使用0.55nm的EOT制造n-MOSFET器件和0.7nm的EOT制造p-MOSFET期间,结果得到了成功的展示。

评论