多路可编程PWM芯片设计

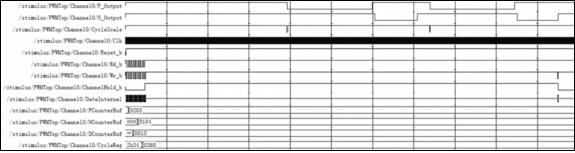

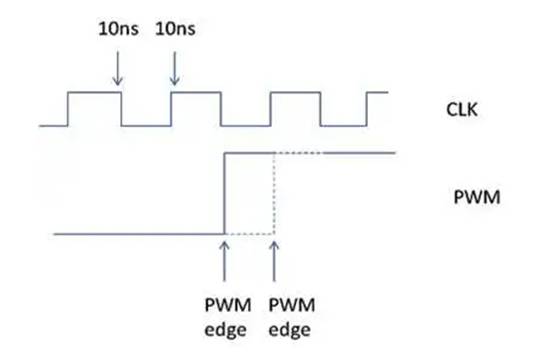

图5 输出结果与程序设定的周期和PWM波形完全一致

从图5中,可以看到PWM输出信号,在ClkGen的CycleScale信号的控制下周期输出编程设定的PWM波形,并能异步响应ChannelHold_b信号的输出控制。

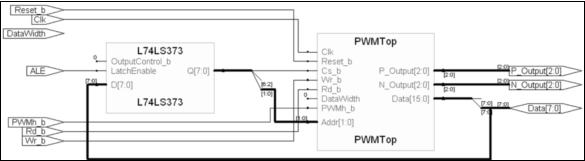

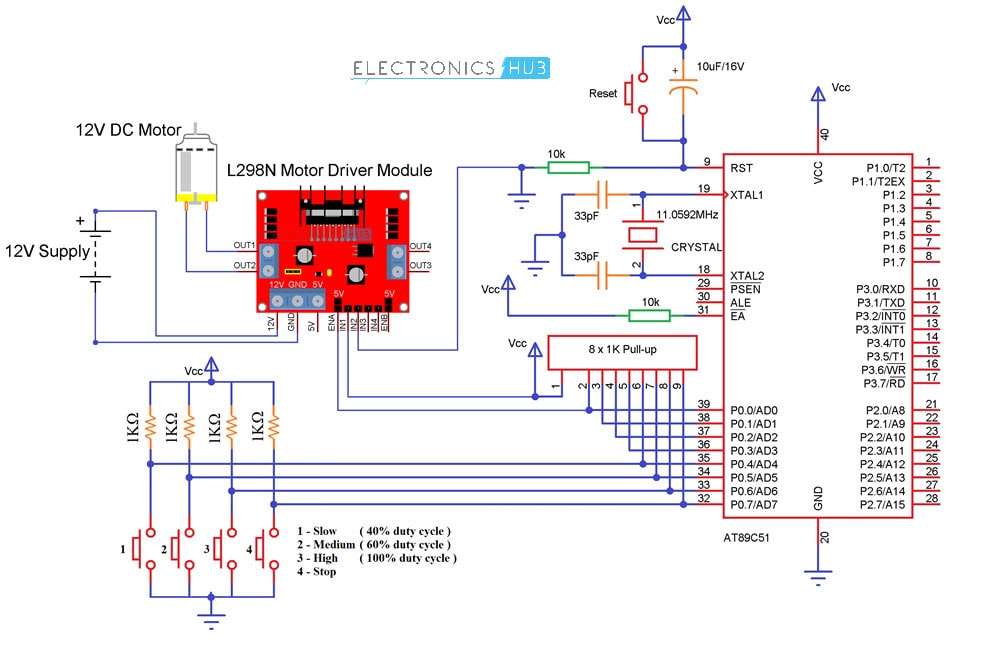

PWM的FPGA验证,采用8bits数据接口,89c51[4]做外围控制器(12MHz),对PWM进行操作。为了方便与单片机接口,将74LS373锁存器内置到PWM中。整个数字设计部分见图6。

图6 PWM+L74LS373电路图(与51单片机验证)

通过Synplify Pro编译后的结果显示:

ProjectTopModule : PWMTopFor8051

Estimated Frequency: 72.9 MHz

Total LUTs: 1478 of 4160 (35%)

占用FPGA资源35%。针对51系列的单片机而言,PWM可运行的频率远超过系统频率。因此在读写时序上可以完全保证整个设计的可靠性。

将编译后的pof文件下载到APEX20KE EP20K100E TQ144-2X(Altera) fpga[5]验证板。采用40MHz的FPGA时钟。根据先前软件仿真的步骤,将读写操作转换为单片机程序烧录到单片机。最后的结果通过示波器我们可以清楚的看到实际输出与设计完全一致。芯片采用.35工艺,一次流片成功后,测试结果显示结果非常理想,实现了当初的设计要求。

参考文献:

[1] MICHAEL D. CILETTI著, 张雅绮, 李锵等译. Verilog HDL 高级数字设计[M]. 电子工业出版社 2005年

[2] 陆庭孝等著, 可靠性设计与分析[M]. 国防工业出版社, 1996年

[3] ModelSim Book Case, Mentor Graph 公司, 2006年

[4] 沈庆阳等著. 8051单片机实践与应用[M]. 清华大学出版社, 2003年

[5] EDA先锋工作室, 吴继华, 王诚编著. Altera FPGA/CPLD 设计 (高级篇)[M]. 人民邮电出版社, 2005年

pwm相关文章:pwm是什么

pwm相关文章:pwm原理

脉宽调制相关文章:脉宽调制原理

评论