多路可编程PWM芯片设计

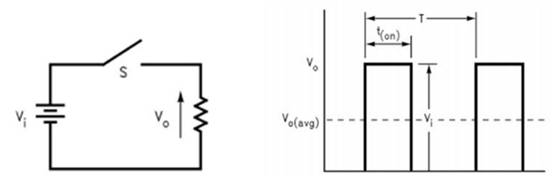

某系统中的H桥驱动电路采用2路脉宽调制器(PWM)信号驱动一个电机来控制其正,反两个方向的运转,且两路信号必须有一定的时间间隔来避免驱动电流过大损害驱动元件。为使其能灵活应用,针对系统要求,PWM控制器应具备以下功能:

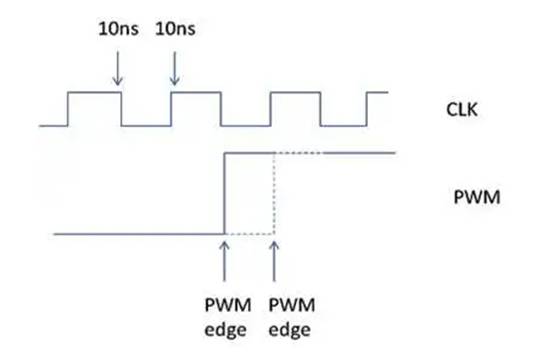

本文引用地址:http://www.amcfsurvey.com/article/94604.htm·3路独立PWM输出,每路输出2个驱动信号,周期、占空比、死区时间可编程,对应10MHz系统时钟,周期为1μs-6.5536ms;

·精简地址线,节省外围引脚及地址资源占用;

·提供与8/16bits单片机的双向数据接口,内置地址/数据锁存器。

PWM结构规划

在采用自顶向下(Top_Down)正向设计中,芯片的结构划分,规格定制是整个设计中最重要的环节,合理的结构设计将决定整个设计的成败[1][2]。

PWM输出信号的周期、脉宽、死区时间等参数可以通过加载内部的寄存器来实现,写入PWM芯片的数据分数据字与控制字两部分。由内部控制逻辑模块来处理控制字信息,并译码产生各内部通道内部信息寄存器的片选信号。数据字通过内部数据总线在各通道模块传递PWM的特征信息数据。

芯片内部的各模块通过内部片选结合读写使能完成数据交换。芯片与外围控制器进行数据交换时采用双模式接口(8/16bits),可通过外置选择引脚DataWidth来选配。

芯片的核心是由3个完全独立且相同的通道模块构成。通道内部的数据接口将完成外部读写逻辑(RWLogic)传输到内部数据总线的数据收发工作。PWM周期生成模块(ClkGen)则依据写入的周期信息,输出PWM的周期控制信号。

PWM输出由通道状态机完成,通道接收到PWM信息数据后,进行数据校验,合格的数据将在合适的条件下启动状态机,并在不同的状态下完成PWM输出。不合格的数据将被忽略。

地址/数据锁存则依据通用74LS373的逻辑功能,编写一个完全可替代的L74LS373来实现。

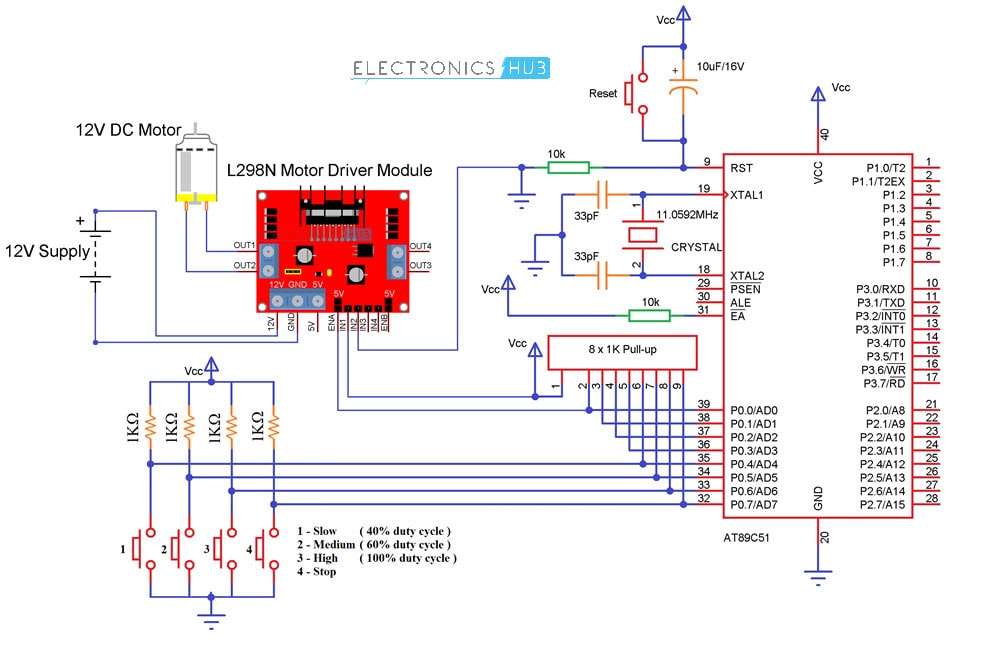

根据总体构建思路,最终的芯片总体结构图如图1所示。

pwm相关文章:pwm是什么

pwm相关文章:pwm原理

脉宽调制相关文章:脉宽调制原理

评论