多路同步串口的FPGA传输实现

信号抗干扰处理

本文引用地址:http://www.amcfsurvey.com/article/94602.htm在FPGA和ARM之间的通讯中利用差分信号传输用于消除信号的干扰。差分对是指两条线路总是传送相反的逻辑电平,差分对信号对外界干扰源产生的噪声不敏感,例如电路板的干扰噪声等。

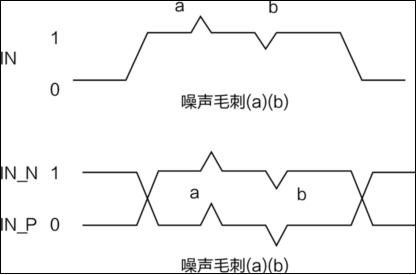

如图7所示[5],IN引脚连接一个信号源,可以看到,对a噪声毛刺不敏感,但是对于b噪声毛刺,却有可能使其误认为一个脉冲,而这个可能引起FPGA内部的一些不期望的行为,如读出一个错误的值。

图7 差分降噪处理原理

差分对中的两个信号总是传送互补的逻辑值,所以当上图中的IN_P为逻辑1时,IN_N则为逻辑0,反之亦然。并且布线时,差分对的两条线路布线得非常的近,因此噪声对他们的影响都是相同的。接收端只对两个信号的差异感兴趣,若两个信号相同,则对此不敏感。

评论