多路同步串口的FPGA传输实现

当接收模块有请求时,发送模块即将接收模块采集到的数据写入发送模块的缓存FIFO中,将其称之为S_FIFO。每轮从R_FIFO中传输的8个数据均依次存入S_FIFO中。

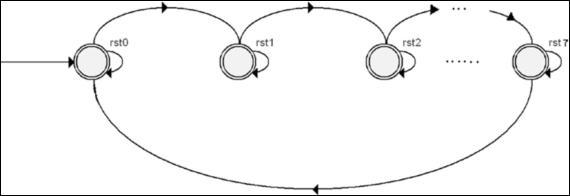

本文引用地址:http://www.amcfsurvey.com/article/94602.htm因为DSP的8个同步串口均同时工作,可以认为当有一个输入模块的数据接收完毕时, 8个端口的数据均应该接收完毕,保险起见,可以延时若干时钟周期后开始接收数据。从端口0至端口7为一轮,若此时有端口没有数据,即可认为此端口暂无数据输出,用数据0替代,发送模块继续接收下一个端口的数据。用状态机来实现此功能,如图4所示。

图4 S_FIFO写操作的状态机图

发送模块完成FPGA向ARM的数据传输,当FPGA发送模块S_FIFO中的数据达到一定数量时,FPGA即向ARM发出发送数据请求,ARM即开始对FPGA进行数据的读取。

FPGA中的S_FIFO同样也是异步FIFO。写时钟由锁相环提供100MHz;读时钟由ARM的读取使能信号OE取反得到,读使能由ARM的片选信号NGCS取反得到。ARM读取数据会产生NGCS与OE低电平信号,无操作时置高。每次读取数据时NGCS与OE先后置低,取反接至S_FIFO读端口分别为NGCS_N与OE_N。对S_FIFO读取时,每当读时钟OE_N为上升沿,读使能NGCS_N必为1,完成一次读取操作。

这样实现了ARM与FPGA之间的跨时钟域数据传输。FPGA发送数据采取乒乓操作, ARM可以源源不断的将S_FIFO中的数据读取出来。FPGA和ARM的数据传输原理图如图5所示。

评论