高性能多DSP互连技术*

数据的串行化意味着数据必须以分组方式传输。而由于信号完整性问题,高速串行差分线一般不允许多点负载,因此基于SerDes的互连一般是点到点的直接互连。当DSP数量较少时,可以采用DSP间两两的直接互连;当DSP数量较多时,须要采用中间DSP或用于数据传输的中间器件—交换机。

本文引用地址:http://www.amcfsurvey.com/article/93420.htm

因此,物理层技术的发展推动着高性能DSP的主要互连技术从多点并行总线转向高速串行直连和分组传输交换。例如TI在2008年10月发布的3核DSP TMS320C6474、Freescale在2008年11月发布的6核DSP MSC8156,都已经取消传统意义上的数据、地址和控制三总线接口而代之以sRIO、GE之类的标准分组交换网络接口以及AIF这样的高速直连接口。

根据传输特性对互连技术的分类

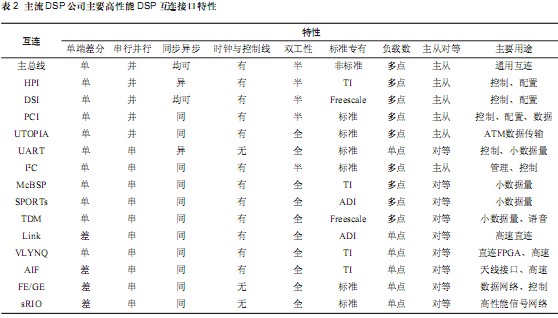

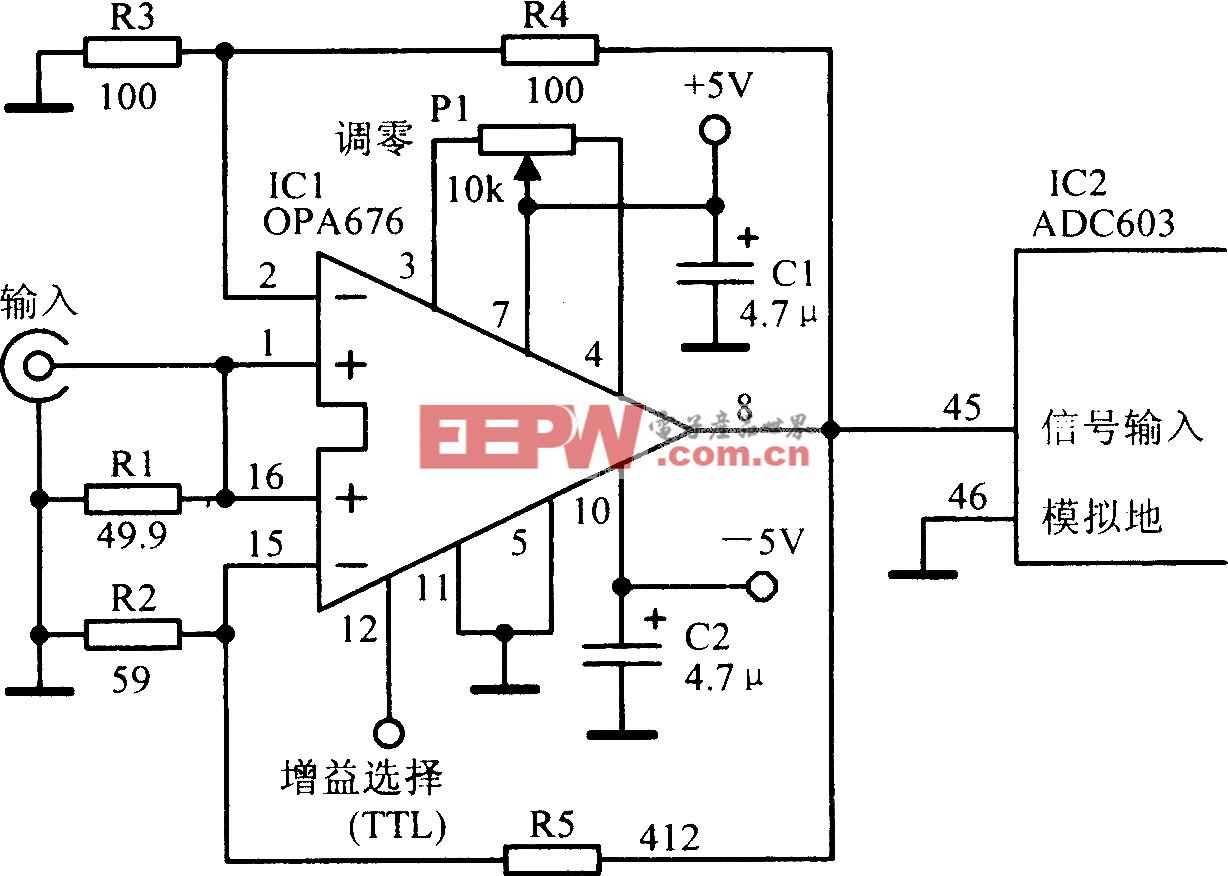

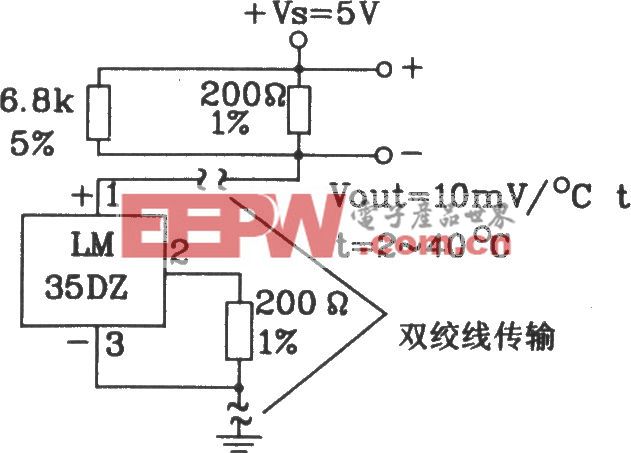

互连的目的满足接口及算法链路的数据传输需要,因此互连特性往往与传输特性紧密相关。各种互连技术虽各有不同,但可以根据互连与传输的共性进行统一分类,有助于理解并选择合适的互连技术。表3是根据互连与传输的特性对现有主要DSP互连技术的分类总结。图1~图4是对典型互连技术实例的图示。

评论