高性能多DSP互连技术*

前言

本文引用地址:http://www.amcfsurvey.com/article/93420.htm由于现代数字信号处理器(DSP)设计、半导体工艺、并行处理和互连与传输技术的进步,现代高性能DSP的处理能力得到极大发展。但在移动通信、雷达信号处理和实时图像处理等复杂电子系统中,单片DSP的性能仍可能无法满足需求,通常需要使用多片DSP构成并行信号处理系统。

在多DSP系统中,互连技术连接DSP、接口及其他处理器,一起构成系统的静态体系结构,是数据传输的中间介质的总和。互连技术传输代表计算任务、中间数据、结果或状态控制信息的数据流,使接口与DSP中的算法模块通过数据流动态地连接起来,整合成分工协作的有机整体。

已经有一些对多DSP并行系统互连技术的综述[1][2] [3][4][5][6],但还不够全面而且没有反映高性能DSP互连技术的最新进展。因此,本文以世界主流公司的典型高性能DSP产品为例,全面总结概括高性能DSP的互连接口技术及其发展,对其互连特性进行总结和归纳分类,在此基础上全面总结给出并行信号处理系统中多DSP互连设计的总体设计考虑和实际经验。

高性能DSP互连接口技术及其发展

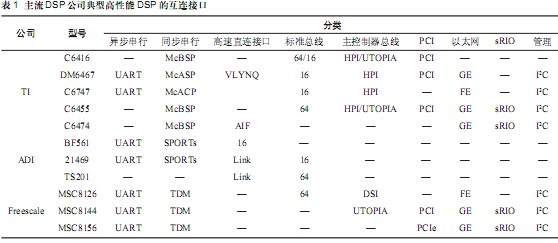

多DSP系统的互连以DSP自身接口为基础,下面以TI、ADI和Freescale三家公司的高性能DSP为例系统概括现有的DSP互连接口,见表1。

现有DSP的互连接口在物理层和传输控制上的特性是选择使用互连技术的基础,表2是对表1中所有的DSP互连接口的互连特性的总结。

表1 主流DSP公司典型高性能DSP的互连接口

可以看出,在越来越高的传输速率需求的推动下,高性能DSP互连接口在物理层技术的主要发展趋势是:从高电压摆幅→低电压摆幅,从单端信号→差分信号;从并行总线→串行信号线;从收发异步→收发外同步→源同步→串行码流中嵌入时钟的串行器/解串行器(SerDes);从半双工→全双工;从多点分时共享总线→点-点的专用互连;最终使接口传输速率从几十Mbps发展到目前的10Gbps。

评论