基于XC2C64A芯片的无线录井绞车信号检测电路设计

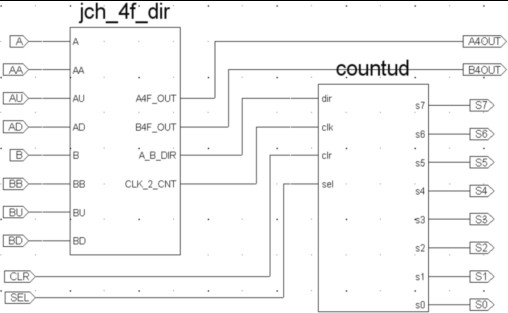

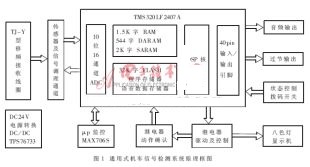

根据如上的设计原理,采用Xilinx公司的EDA软件ISE和模块化设计[4]的方法设计了无线录井绞车信号的检测电路,其顶层设计电路如图2所示,该电路包括两个子模块:倍频、鉴相子模块jch_4f_dir,具有4倍频和方向鉴别功能;16位二进制可控加减计数与数据接口子模块countud,具有加/减计数(由方向鉴别信号控制)和MCU选择读取高/低8位计数数据等功能。该电路在XC2C64A-7VC44I器件[5]上进行了下载测试。

本文引用地址:http://www.amcfsurvey.com/article/93391.htm

图2 绞车信号四倍频、鉴相与计数顶层电路图

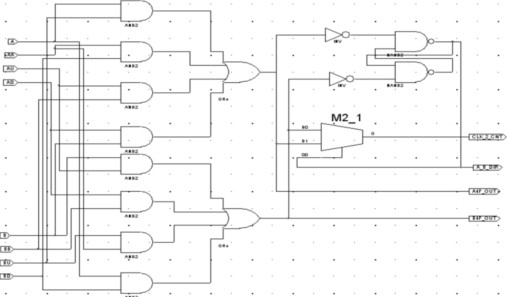

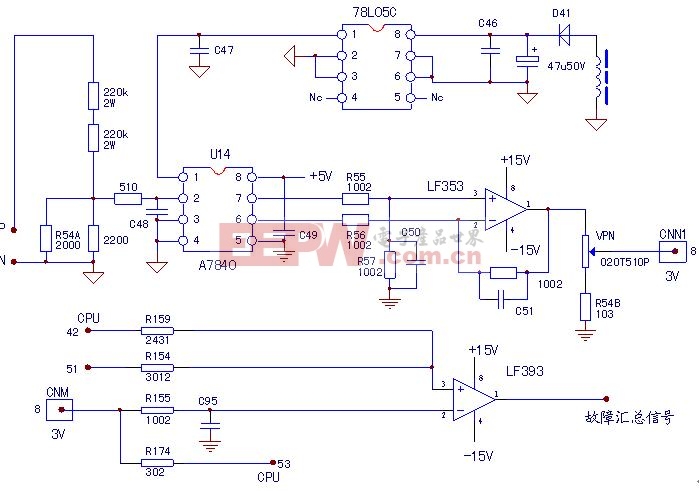

A、B、AA、BB、AU、AD、BU、BD共8路信号经过如图3中左侧所示的倍频电路,产生4倍频的脉冲信号,给后面的计数器提供计数时钟信号;如图3中右上侧所示的由与非门组成的RS触发器,是鉴相(方向鉴别)电路,可以得到反映绞车传感器A、B两相信号到达先后的方向信号A_B_DIR。假设绞车正转,A超前B,A_B_DIR=1;绞车反转, B超前A,A_B_DIR=0。

鉴相(方向)信号A_B_DIR一方面连接到二选一数据选择器的选择输入端S0,用来控制A4F_OUT和B4F_OUT选通到如图2右侧所示的计数器countud进行计数,当A_B_DIR=1(A超前B)时,clk=A4F_OUT(有脉冲输出);当A_B_DIR=0(B超前A)时clk= B4F_OUT(有脉冲输出);同时,A_B_DIR也控制计数器进行加法(A_B_DIR=0)或减法(A_B_DIR=1)计数。

图3绞车信号四倍频与鉴相电路图

16位二进制加/减计数器的主要功能设计描述如下所示(采用Verilog HDL)。其中,clk是计数时钟输入端,clr是异步清零端,dir是加减计数控制端:dir=1,减法计数,dir=0,加法计数;sel是计数数据读取控制端,由单片机给出的选择信号实现高8位、低8位的计数数据输出,sel=0,低8位,sel=1,高8位。

无线录井绞车倍频、鉴相与计数电路的仿真测试

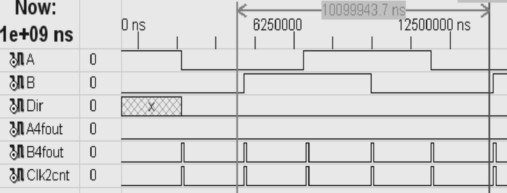

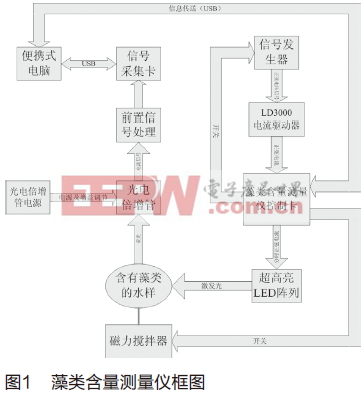

在Xilinx的ISE环境下对倍频、鉴相子模块jch_4f_dir的仿真波形图示于图4。该波形是绞车传感器输出B相波形超前A相波形90°时的仿真结果。此时,倍频输出信号B4fout与A(或B)信号的频率成4倍关系,鉴相(方向鉴别)输出信号Dir=0,这与前面的原理分析完全一致。

图4 B超前A的四倍频与鉴相输出信号波形图

隔离器相关文章:隔离器原理

评论