利用频域时钟抖动分析加快设计验证过程(07-100)

——

图8 利用交叉关联技术获得的出色抖动本底噪声

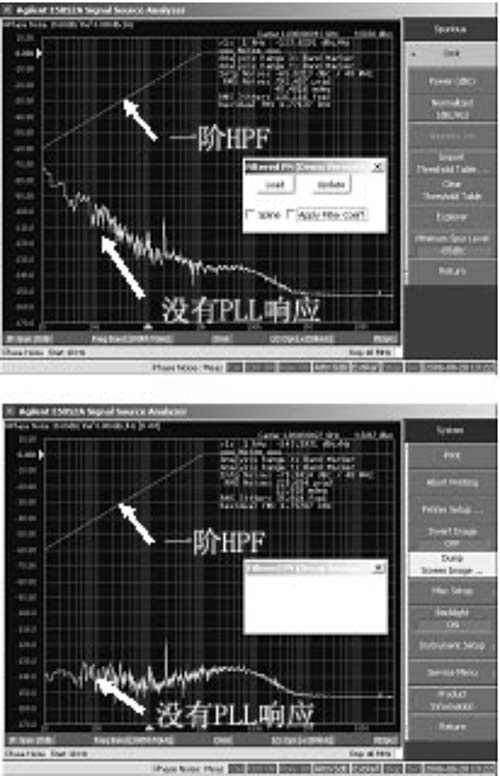

实时仿真PLL响应

图9表示直接应用于时钟相位噪声信号的PLL响应功能的结果。您可以看到如何消除频谱的不同部分,使您可以分析与应用相关的抖动。E5052B对相位噪声测量的实时抖动分析功能可加快您的设计进程。E5052B SSA可以导入任何PLL响应函数,使您可以轻松快速地仿真设备到设备的PLL响应。

图9 仿真PLL响应

结语

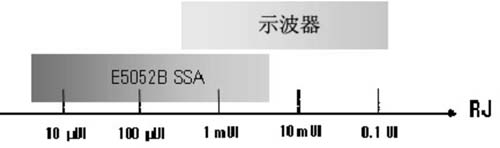

对于高速串行数据应用,时钟抖动分析的主要目的是确定参考时钟的抖动对系统比特误码率的影响。最精确的方法是对时钟应用发射机(和接收机)在最坏情况下的传递函数,并测量获得的时钟RJ和PJ。在E5052B上运行的E5001A精确时钟抖动分析软件改变了传统的抖动测量方式,它不仅能以飞秒级分辨率对时钟抖动进行全面分析,而且具有出色的易用性和实时抖动分析功能,可以帮助您加快设计验证过程。

评论