使用FPGA测试的一些有效方法(05-100)

综合过程解决时序问题

本文引用地址:http://www.amcfsurvey.com/article/91577.htm我们使用Synplicity公司的Synplify工具进行综合,这是业界通常使用的综合工具之一。选择该工具最主要的原因在于它与Xilinx的FPGA配合的很好。我们做过实验,通过该工具综合产生结果报表,再通过ISE产生真实布局布线后的报表。对这两个报表的时序估计部分进行对比,我们发现两者之间惊人的相似,最差路径之间的差别不超过1ns。

综合的时候需要设置约束,最重要的是时钟约束。这个约束限制了系统工作的频率。为了降低系统对于时钟抖动的敏感性,我们采取的第一个方法是在设置时钟约束的时候将此约束值设的略高于实际的时钟频率。这样做有一个前提,那就是在综合后不得有负的时钟余度(time slack)出现。当没有负的时钟余度出现的时候,提高时钟约束可以有效避免因时钟抖动而引入的时序问题,但是如果因为提高了约束中时钟频率,而导致负的时钟余度的出现,那么有可能导致在布局布线过程中产生时序冲突而无法正常布局布线。在这种情形下,就不宜提高约束中的时钟频率。

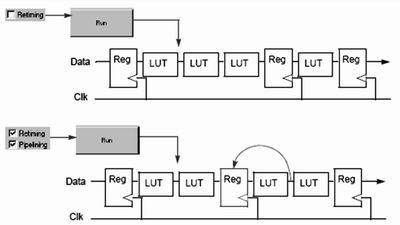

在综合中采取的第二个方法是使用综合工具提供的pipeline和retiming功能。这些功能可以调整寄存器的位置,使之在不改变逻辑的前提下,将寄存器的位置调整的更加合理,如图2所示。这个功能主要用于组合逻辑过长且不合理的情况下。当然,如果某些乘法器位数过宽而结果没有寄存的时候也会导致组合逻辑时序紧张。当发生这种情况而retiming功能又无法纠正时,就需要设计者在做设计的时候对乘法器的输出结果做一拍寄存,同时其余的控制逻辑也要做相应的调整。

图 1 DSP48示意图

布局布线阶段解决时序问题

当综合工作完成,进入布局布线的阶段后,仍然有两种方法可以改善逻辑时序问题。

第一种是手动增加并调整BUFG(Global Clock Buffer)。BUFG是Xilinx的全局时钟资源,所有时钟树的起点都是BUFG,位于FPGA的北极和南极。当布线后仍有负的slack时,有可能是某些当作时钟使用的信号没有被放上时钟树,此时就要手动将这些信号放上BUFG。若遇到门控时钟,还应该使用BUFGMUX资源。另外,在Virtex-4中,北部的BUFG主要负责北部的时钟,南部的BUFG负责南部的时钟。在我们的项目中,共有十余个时钟,因此,BUFG位置的选择也很关键。有些时候,工具不能解决一切问题,只有手动调整BUFG的位置,或将BUFG的位置信息写入用户约束文件才可以取得较满意的效果。

评论