3G中的CMOS基RF集成(05-100)

多RF前端系统集成方案

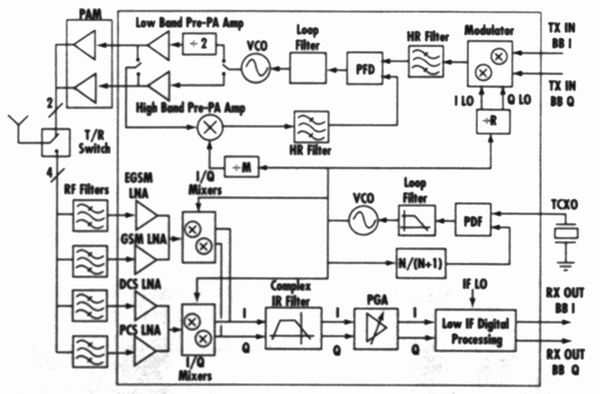

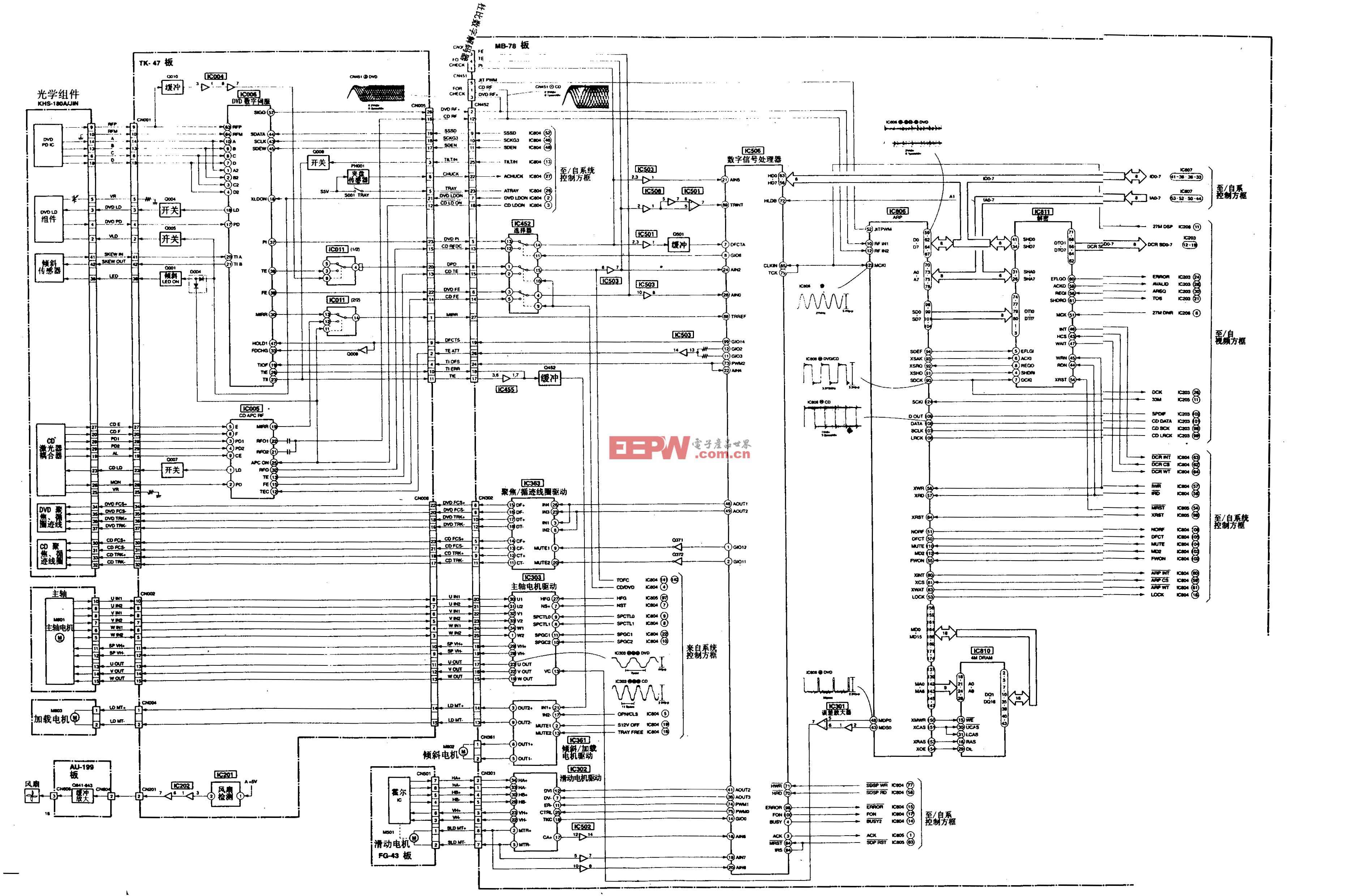

本文引用地址:http://www.amcfsurvey.com/article/91467.htm4频段GSM/GPRS系统的RF前端设计方案示于图2,用一个高集成度单片CMOS收发器。天线开关模块连接到发送和接收通路,对每个GSM频段用接收器SAW滤波器和相关的匹配电路。发送通路至少需要两个PA:一个PA用于GSM-850MHz和E-GSM-900MHz频段,第2个PA用于1.8GHz DCS和1.9GHz频段。

很多可用的集成RF前端模块可降低元件数并简化设计。它们包括带动率放大器和功率控制逻辑功能(PA模块)的模块和带PA及开关功能发送模块 。在接收端,由SAW滤波器单元和带多路开关和接收滤波器的RF前端模块组成。

与图2中的GSM/GPRS系统相比,图1 3G多模系统的更复杂前端设计支持2.5G和3G RF信号传输。增加多路转换器是必须的,因为WCDMA是基于频分双工,发送器和接收器是同时开关转换。然而,像GSM/GPRS那样,经济定标将带来前端元件集成。

当今蜂窝基站结构分成两种:基带功能分成分离模拟和数字基带芯片或单片高集成CMOS SoC器件(包含实现模式和数字功能)。因为,每种方法具有截然不同的优点,所以在两种分配方法之间进行选择,取决于为大多数经济平台方案选择未来集成路线等因素。

尽管单片方法节省PCB真正的面积,但用分离的模拟和数字基带芯片,对于集成是最可取的道路,因为它使模拟基带功能与实现数字基带的“纯”数字电路隔离。两片方案也能使数字基带定标更小的CMOS几何尺寸,同时集成其CMOS平台元件(如应用处理器,图像处理器,存储器)

基带结构的一种趋势是简单地去掉模拟基带芯片,于是使数字基带功能集成最佳,同时简化无线到基带芯片接口设计。此方法在无线和数字基带之间,采用一个高速数字接口。可以规定此接口为串行或并行。串行接口降低了器件引脚数,但增加了高速缓冲器芯片上的晶体管数。并行接口增加引脚数和封装尺寸,但在硅中可更有效地实现。

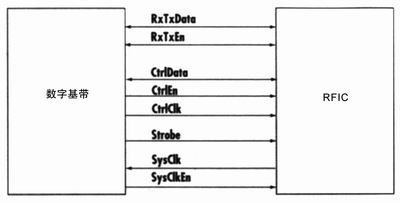

现在,DigRF Standards Body 为2.5G规定了标准高速串行接口规范(见图3)。当支持数字接口时,无线设计将增加复杂性。它不仅仅必须执行模拟到数字和数字到模拟的转换,而且必须有接口逻辑来处理基带的数字通信。用CMOS工艺技术比其他工艺更容易、更经济地实现这些功能。

图3 无线和数字基带之间的2G DigRF接口

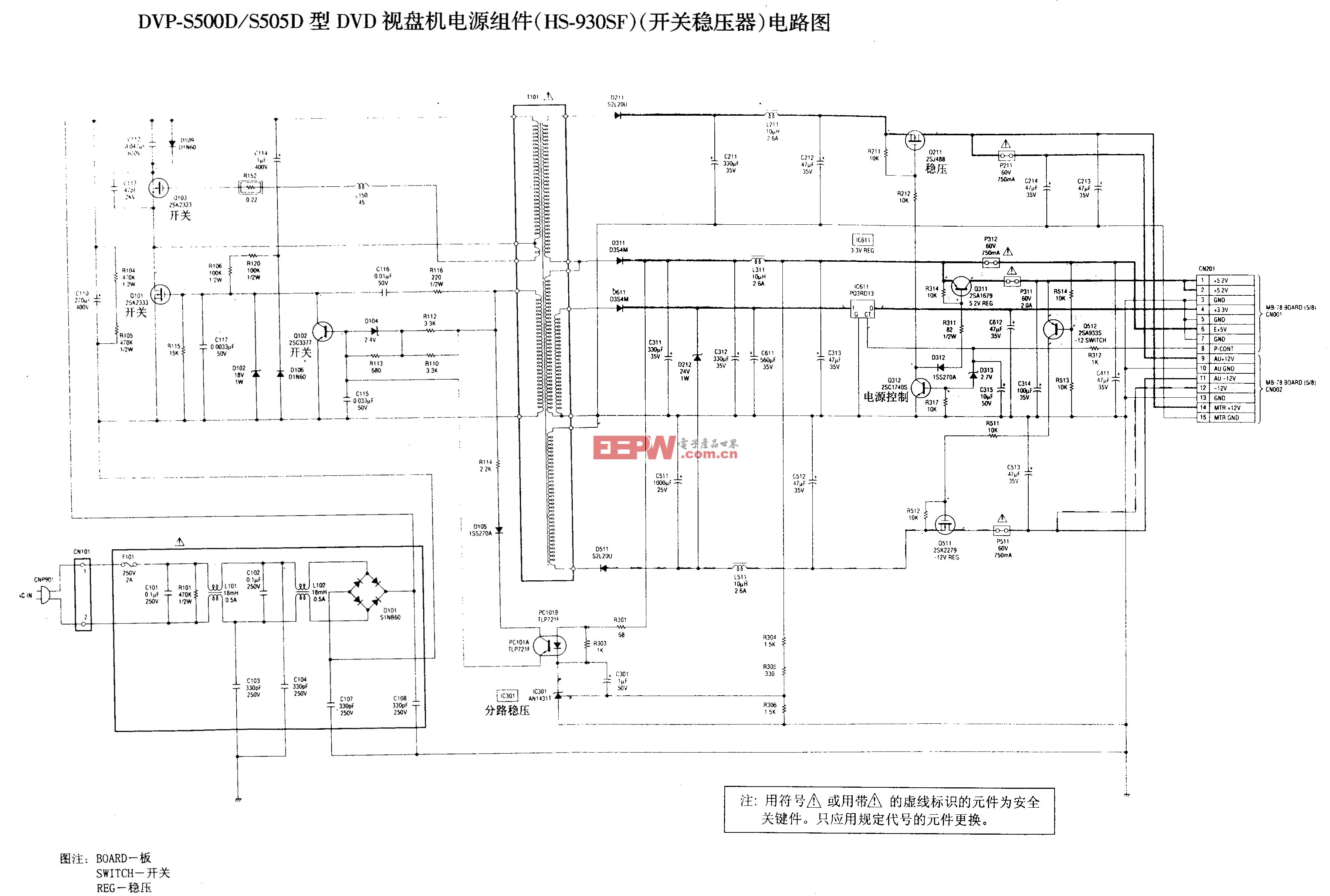

图4 单片4频段CMOS收发器框图

评论