高速信号、时钟及数据捕捉(05-100)

随着模/数转换器的数据转换取样率提高至每秒千兆个取样 (GSPS) 以上的水平,数据转换系统必须作出相应的配合,才可支持这样高的转换率,而其他支持性的模拟元件也必须产生系统所需的高频信号,然后将之放大。系统设计工程师除了要对模拟信号路径有深入的了解之外,也要彻底认识取样时钟以及系统如何以高位速率捕捉数字信号。本文 将会就有关上述两个重要的问题提供多个不同的解决方案。以下所讨论的资料有助深入了解采用高性能模/数转换器的系统。

本文引用地址:http://www.amcfsurvey.com/article/91444.htm时钟电路

时钟电路是高速数据转换系统最重要的子电路之一,因为时钟信号能否准确定时会直接影响模/数转换器的动态性能。为了减低其影响,模/数转换器时钟电路的定时抖动或相位噪声必须极低。若选择时钟电路时没有将这个因素加以考量,那么即使所采用的前端模拟输入电路或模/数转换器性能非常卓越,系统性能也可能会不如想象中理想。完美的时钟永远可以在精确的时间内提供跳变沿。但实际上,时钟沿会不断出现在不同时间内,正因为时间的不确定性,取样后波形的信噪比受到数据转换过程的影响。

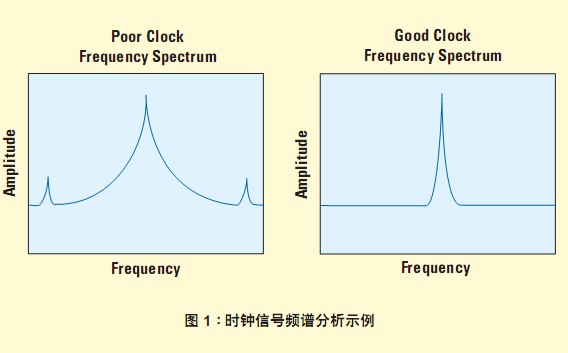

图 1 时钟信号频谱分析示例

只要因为抖动产生的噪声不超过量化噪声(1/2 LSB ), 最大的时钟抖动能适应任何抖动源,其数值可以用下式计算出来:

Tj(rms) = (VIN(P-P) / VINFSR) x (1/(2(N+1) x x fin))

若输入电压 (VIN) 范围能够完全吻合模/数转换器的满幅值范围,抖动便会成为影响模/数转换器分辨度 (N 位) 及输入频率(fin) 的因素。

若输入频率不超过奈奎斯特率 (亦即若转换率为 1GSPS,输入频率为 500MHz),总抖动要求的公算公式如下:

Tj(rms) = 1 x (1/(2(8+1) x x 500 x 106))

Tj(rms) = 1.2ps

这个数值代表不同抖动源的抖动总和。来自模/数转换器芯片本身的抖动称为孔径抖动。它与芯片的输入取样及保持电路定时上的不确定性有密切的关系。若要确定时钟电路可承受的最高时钟抖动,这个不确定因素必须一并加以考量。

时钟电路抖动 = SQRT (Tj(rms)2 - (模/数转换器孔径抖动)2 )

以 ADC08D1000 芯片为例,数据表上列出的孔径抖动为 0.4ps,这个数值将模/数转换器时钟对抖动的要求限制到约为 1.1ps。

但是,简单的让振荡器的性能参数符合要求并不能保证整个系统能达到预期的效果。因为与基本频率并存的其他频率也发挥极为重要的作用,所以我们必须利用频谱分析仪检视时钟信号,并确保基本频率能量不会在频谱范围内过宽。扩散至较高频率范围内的杂散信号不但可以在分析仪上清楚看到,而且还会直接影响抖动。图 1 将非理想时钟信号的频谱与低噪音、低抖动时钟信号的频谱加以比较。

评论