单片彩色LCoS显示系统的设计实现

1 引言

硅上液晶显示(Liquid Crystal on Silicon,LCoS)技术是CMOS半导体集成电路和液晶显示相结合的技术。LCoS技术具有如下优势:

(1)可以利用标准CMOS工艺和成熟的LCD工艺线;

(2)物理尺寸可以做的非常小;

(3)即使像素尺寸非常小,仍可以得到非常高的开口率。

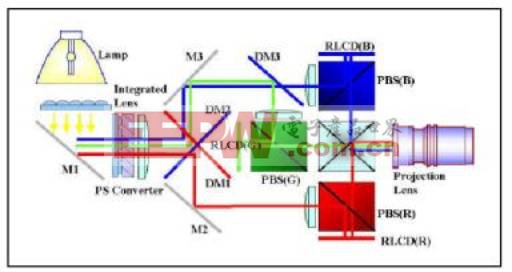

由于其技术和制造优势,LCoS技术有着广泛的应用前景。由于其尺寸小、功耗低、分辨率高,可以用作移动通讯等设备的显示屏,如头盔显示。目前彩色LCoS显示系统主要分为单片和三片式系统2种,单片式系统对于三片式系统主要有以下优点:体积小,成本低,易于实现小型化;三片式需要像素校准,而单片式则不需要。本文主要讨论单片彩色LCoS显示系统的设计与实现。

2 显示原理

三片式彩色LCoS显示系统利用空间混色实现彩色显示,而单片式彩色LCoS系统只用1片LCoS芯片,分时扫描红、绿、蓝3个子场的图像,并且在每个子场结束的时,分别将对应颜色的背光灯打开,利用人眼的视觉残留效应实现彩色显示。当子场的频率越高,图像的闪烁程度就越低。

3 系统总体概述

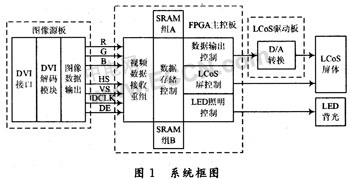

单片彩色LCoS整个系统的框图如图1所示。

在整个系统的最前端是1块以AD9887A为主芯片的图像源板,该板负责对DVI信号进行解码,解码后的信号交由后面的FPGA板进行处理;FPGA板除了对图像数据进行重组外,还需要产生LCoS驱动板和LCoS芯片所需的时序,FPGA芯片使用Altera的EP1C6,另外板上还有2组6片SRAM作为图像数据的缓存;LCoS驱动板的任务是进行D/A转换,驱动LCoS芯片模块进行显示,该驱动板包括D/A芯片AD8381和LCoS芯片的电源模块;LCoS芯片模块则包括LCoS显示芯片、LED背光模块以及光学组件。

4 主要芯片介绍

主控板的核心器件FPGA采用Altera公司的EP1C6Q240C8,该器件包括5 980个LE,80 kb的内部SRAM,2个内部PLL,最大可支持185个用户I/O管脚。经过评估,其丰富的资源可以很好地完成LCoS的主控单元的所有功能,包括:接收前级转换好的视频数据,处理后保存到一组RAM中,同时从另一组RAM中读出处理好的数据送至D/A,并控制D/A转换,产生LCoS的上屏时序和LED光照系统的控制时序。

板载SRAM采用ISSI公司的IS61LV10248,用作图像数据的缓存,单片容量为1 M×8 b字节。本系统共使用6片这样的SRAM。分为2组,每组3片,进行乒乓操作。每组SRAM地址线共享,数据线位宽扩展为24 b。

本系统D/A转换采用Analog Device公司的AD8381。该芯片支持高达100 MHz的10 b数字输入,6路9~18 V电压的模拟输出。其典型时序如图2所示。图2中DB(0:9)是输入的数字信号;CLK是采样时钟;STSQ表示新的一组数字信号的开始;XFR表示开始一次转换,其下降沿有效。本系统采用的LCoS芯片为8路模拟输入,因此这里采用2片AD8381,每1片用到其中的4路。

根据图2中的时序,并考虑到实际情况,具体应用如下:每个周期同时向两个AD8381的数据口发送一个像素数据,4个周期后进行数据锁存,由STSQ和XFR这两个控制信号控制,这样同时得到8个像素的像素值,而不需要如图2那样发送6个数据后再进行一次转换。输出的模拟电压值在下一个锁存信号的下降沿完成转换。STSQ和XFR这2个管脚由同一个FPGA管脚驱动即可。在其他管脚中,E/O信号和R/L信号分别用于选择时钟信号是上升沿有效还是下降沿有效和像素数据发送顺序,这里设计成外部跳线。另一个控制信号INV用来确定图像数据电压是正信号还是负信号的,由于液晶的特性,在每帧开始时将其取反。而AD8381的参考电压VMID和屏的参考电压VCOM连接在一起,在INV的配合下,实现对屏的交流驱动。

5 FPGA程序设计

5.1 模块划分

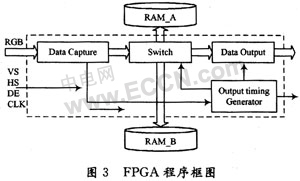

整个FPGA程序的模块框图如图3所示。主要包括:D/Ata Capture模块,负责将输入的数据按一定的格式顺序存放到SRAM中;Switch模块,负责控制RAM的切换;D/AtaOutput模块,负责从SRAM中读取数据按照一定的格式发送出去;Output timing Generator模块,负责生成输出的控制时序,并且控制D/Ata Output模块的输出和Switch模块的切换,而该模块的工作是受到D/Ata Cap-ture模块控制的。

5.2 存储安排

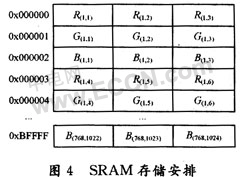

为了获得较大的数据位宽,并且考虑到FPGA管脚数量,用于缓存图像的SRAM选用的是3片1 M×8 b容量的,作位扩展,这样可以存放下完整的1帧数据。具体说就是每个地址存储的大小是3个字节,可以用来存放3个像素的数据(同种颜色)。地址0x0放置3个像素的红,而地址0x1存放3个像素绿,地址0x2存放3个像素蓝,而这3个地址的3个像素在屏幕上是第一行的第1,2,3个像素,接下来地址0x3又存放了3个红色像素,如此循环,直到地址0xBFFFF存放最后3个像素的蓝色数据。如图4所示。

5.3 算法流程

(1)D/Ata Capture模块的数据转存算法

D/AtaCapture模块负责将输入的数据按一定的格式顺序存放到SRAM中。每个时钟从AD9887A板过来的数据是24位的RGB数据,8位红,8位绿,8位蓝,而实际输出的时候是按照1帧红1帧绿1帧蓝的顺序输出的。因此如果能将读入的24位RGB数据按照一定的格式存放,就可以方便的读取数据,格式如图5所示。

具体的转换是通过一个状态机实现,其中有6个24 b的寄存器r1~r6用来缓冲6个像素的RGB值。用6个状态完成类似矩阵转换的任务,每个状态会输出1个24 b的转换好的数据,并生成地址,即每个状态都会将1个24 b的数据存入到SRAM中,而这24 b就是3个像素的同一种颜色的值。

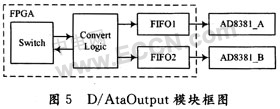

(2)D/Ata Output模块数据输出算法

D/Ata Output模块是数据输出模块。每个时钟周期从SRAM中读取到的是3个像素的数据,而每个时钟发送到每个AD8381的是一个像素数据,因此是不同步的,需要使用双时钟FIFO作流量控制才能使数据正确传输,具体的读取操作:如图5所示。像素0~3放入FIFO1,像素4~7放入FIFO2,这样依次下去,每个FIFO放人4个像素。每个时钟放2个像素。该处理任务由Convert Log-ic子模块完成。还要注意的是由于每种颜色的数据不是连续存放的,因此下一个地址的值是加3而不是加1。

6 实验结果

经过对比实验证实,在子场场频比较低的时候,单片彩色LCoS显示系统的闪烁程度会比较高。由于条件所限,研究中选用的LCoS芯片所支持的最高场频为120 Hz,该芯片是为三片式LCoS系统设计的,因此用在单片彩色系统中具有一定的局限性。实验中FPGA程序可以实现90 Hz,120 Hz和180 Hz三种子场频率。在相同的背光源条件下,90 Hz场频时的色彩相对于其他两种要好些;180 Hz时系统也完全能够正常运作,只是色彩稍差,这与LCoS芯片本身有关,不过其闪烁程度已经可以忽略;120 Hz子场时的闪烁还是比较明显的,色彩和90 Hz子场时基本差不多。

因此,要实现单片彩色LCoS显示系统的无闪烁,必须使用较高的子场频(不低于180 Hz),有关资料显示,目前已经出现了为单片彩色LCoS系统设计的LCoS芯片,其支持的场频可达360 Hz,如果选用这样的芯片,就可以实现无闪烁显示。

就本系统来说,已经获得了不错的显示效果,色彩、对比度都达到了比较好的状态,而且闪烁程度也非常低。如果要获得更好的显示效果,就要选择支持更高场频的LCoS芯片。另外,由于该LCoS的响应时间比较长,在屏幕的上沿和下沿还有微弱的色彩混叠现象,这也可以通过选用支持高场频的LCoS芯片来解决。

7 结 语

尽管本系统已经取得了不错的显示效果,但是还不是很完美,还必须采用新型的LCoS芯片。而对于这种最高支持360 Hz场频的LCoS芯片,对硬件速度和D/A的速度都提出了较高的要求:如果源图像的场频为60Hz,而每个子场的频率为360 Hz,则应该有2帧图像相同,同时每个子场的时间缩短为原来的一半(与180 Hz子场频率比),需要数据发送数率和D/A速度至少要快一倍。但是这样的好处就是使本系统所存在的闪烁和色彩交叠显现的到彻底解决,使单片彩色LCoS系统的显示质量趋于完美。

本文主要介绍视频显示系统的硬件结构,以LCOS显示芯片的驱动时序要求为设计标准,提出一种基于FPGA的解决方案,使得系统具有灵活性和可修改性,方便以后的升级以及维护。并对FPGA程序的算法做了详细的介绍。最后对系统存在的问题做了讨论,并提出一些解决方法,以及对未来系统的展望。

评论