基于FPGA圆阵超声自适应波束形成的设计

1 引 言

本文引用地址:http://www.amcfsurvey.com/article/87581.htm在雷达及声纳信号处理系统中,波束形成算法通常采用DSP软件编程实现,控制逻辑电路采用CPLD来完成,这种方法具有软件编程灵活、功能易于扩展的优点,但对于实时性能要求很高的系统,如雷达、声纳探测和超声成像等系统中为了提高对目标变化实时跟踪和测量,就必须尽量缩短信号处理的时间,过长的运算处理时间会对水下目标的探测性能产生较大的影响。声纳工作环境中总存在着各种干扰(例如本舰辐射噪声、近场其他船只的干扰等),普通波束形成系统是一种预形成波束系统,当他处在各向同性、均匀韵噪声场时,可能具有相当好的检测能力,但是出现近场干扰,或者背景噪声有某种不平稳性,声纳的检测能力就会迅速下降,以至完全失去检测能力,而自适应波束形成技术(ABF)就是声纳能够根据周围环境噪声场的变化,不断地自动调节本身的参数以适应周围环境,抑制干扰并检出有用信号。因此采用FPGA来实现自适应波束形成算法是满足复杂海洋环境超声阵列波束形成的较好途径。

最小均方自适应算法(Least Mean Square,LMS)较其他自适应算法具有结构简单,计算量小,易于实现等特点。FPGA实现LMS自适应波束形成算法比采用现有DSP来实现可以明显提高信号的处理速度,节约资源,能更好地满足复杂多变的海洋环境,具有广泛的实用价值。

波束形成系统相当于一个时空滤波器,自适应波束形成系统可采用IIR和FIR两种结构。与IIR滤波器相比,FIR滤波器具有以下优点:可得到严格的线性相位;主要采用非递归结构,从理论上以及从实际的有限精度运算中,都是稳定的;由于冲激响应是有限长度的,因此可以用快速傅里叶变换算法,运算速度快;FIR滤波器设计方法灵活。

本文采用自适应的FIR滤波器结构,结合时延最小均方(DLMS)算法,充分利用FPGA芯片运算速度快,存储资源丰富等优点设计和实现了基于FIR超声阵列自适应波束形成。主动声纳信号为窄带信号,通常采用复数形式表示,在空间滤波器模块采用了循环移位流水乘加器,使复数乘加运算节约了大量资源,同时用并行乘法器完成了DLMS算法,并给出了系统软、硬件模块和仿真分析。

2 超声阵列波束形成系统模型及原理

2.1 系统架构及原理

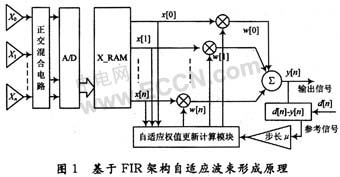

自适应波束形成又称自适应空域滤波,他是通过对各阵元加权进行空域滤波,来达到增强有用信号、抑制干扰的目的,而且他可以根据信号环境的变化,来改变各阵元的加权因子。在理想的条件下,自适应波束形成技术可以有效地抑制干扰而保留期望(有用)信号,从而使阵列的输出信号干扰噪声比(SINR)达到最大。自适应过程的实现可以采用任何一种适用于横向结构滤波器的自适应迭代算法,比如Wiener滤波器,或者最小均方(LMS)算法。本设计采用最小均方(LMS)算法,系统结构原理如图1所示。

基于FIR自适应波束形成系统过程如下:一方面,输入信号与表示在n时刻的值可调节权系数ω1(n),ω2(n),…,ωm(n)相乘后相加得到输出;另一方面,将输出信号与期望信号进行对比,所得的误差值通过一定的DLMS自适应控制算法再用来调整权值,以保证空间滤波器处在最佳状态,实现滤波的目的。

在延时LMS算法(the Delayed LMS Algoritms,DLMS)中,将系数更新延迟几个采样周期,只要延迟小于系统阶数,也就是滤波器长度,则误差梯度▽[n]=e[n]x[n],也就是▽[n]≈▽[n-D],但对于由FPGA实现的乘法器和系数更新需要额外的流水线级,如果引入一个延迟因子D,μ为步长因子,LMS算法就变成:

2.2 系统FPGA软件模块设计

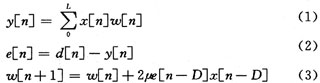

根据数字自适应波束形成的原理和数学模型,本文设计的基于FPGA数字波束形成系统结构如图2所示。8路输入信号x(n)经过前端信号处理,A/D转换后,在总控模块的控制下进入输入数据存储模块双口RAM,自适应波束形成的具体实现步骤如下:

第一步:由式(1)得,实际输入的x(n)和调整后的权值w(n)各分量相乘之后累加得到输出y(n);

第二步:由式(2)得,实际输出的y(n)与期望d(n)相减得到调整误差e(n);

第三步:由式(3)得,延时后的调整误差P(n)跟步长的2倍相乘,再和延时的输入x(n-D)相乘得到的积与延时的权值相加,得到新的权值向量。

第四步:新的权值向量再与新的输入向量循环进行第一到第三步实现自适应。

由此,我们可以将系统分为五大模块:主控模块:主要产生时钟信号,给各模块提供时序信号触发各模块的启动和初始化;双口存储模块(包括输入数据存储模块、权值存储模块、误差信号存储模块等):存储各功能模块所需的数据和参数;自适应权值计算模块,误差计算模块:这两个模块可以合在一起,用于系数更新的白适应算法;空间滤波器乘加模块:完成滤波运算,得到输出结果。

2.2.1 控制模块

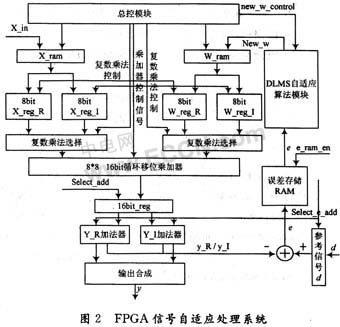

控制模块是整个系统完成功能的控制部件,主要协调各功能模块顺利实现功能,由系统时钟产生时钟脉冲,设计中用分频和有限状态机描述来产生存储器读写信号、滤波运算所用到的控制时钟和复数运算。

输入信号和权值是8位的复数数据,通过控制模块选择乘法操作的操作数,两个复数信号相乘的4种组合00,11,01,10可以完成实部和虚部之间4个乘法运算,四种情况控制模块输出的控制信号分别为ST0,ST1,ST2,ST3。

其中,clk_regbt用来控制乘法器完成乘法,counterbt用来控制乘数的位选,clk_reg用来控制运算新数的进入、上次计算的完毕和结果的输出。

2.2.2 存储模块

存储模块采用8位和16位双口RAM(如图3所示)作为信号数据和权值数据的存入和读取存储器,分别用来存放输入信号x、权值ω和误差e,分别由控制信号clkregbt,clk_regw和clk_rege来控制信号的写入和读出。其中x_ram用来存放输入信号;w_ram存放权值,其输入为系数更新模块的输出,输出为更新后的权值。

2.2.3 自适应处理及复数乘加器模块

数字波束形成器是通过加权因子对空间不同阵元接收信号的加权求和而成的。由于加权因子相当于滤波器系数,而输入的信号为空间位置不同的阵元的接收信号。所以可将数字波束形成器等同于一个空域滤波器来实现。

3 系统仿真与验证

本文设计的核心部分是基于Stratix系列EPlS10芯片设计的分别对I/Q两路原始数据进行DLMS自适应算法和复数乘加运算,在QuartusⅡ环境下用VHDL语言编写了各功能模块,并进行了仿真,共占用了2 703个逻辑单元,同时应用Matlab对数字结果进行波形仿真,以下为仿真验证的结果。

图5为主控模块的仿真波形,其中ST0,ST1,ST2,ST3为复数乘法的4种组合,clk_regbt用来控制乘法器完成乘法,counter_bt用来控制乘数的位选,clk_reg用来控制运算新数的进入、上次计算的完毕和结果的输出。

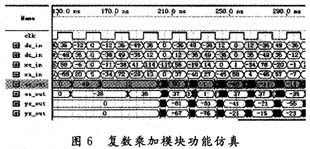

图6为复数乘加模块功能仿真结果,dc_out,ds_out,xc_out,xs_out分别是输入信号和期望信号的实部和虚部,ec_out,es_out,yc_out,ys_out分别为误差和滤波输出的实部和虚部。

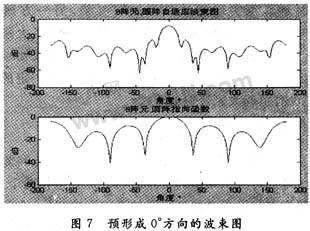

图7为系统仿真测试结果:系统预形成波束方向为0°方向,干扰从45°传来,通过仿真结果可以看出,主波束在0°方向形成,和预形成主波束吻合,在45°干扰方向形成零陷,并且提高了主波束的增益,满足系统的设计要求。

4 结 语

自适应DBF是现代声纳阵列信号处理的关键技术之一,本文介绍了利用FPGA芯片实现的自适应BDF结构,给出了相应的硬件设计和仿真验证,采用FPGA结构,硬件成本低,在自适应阵列信号处理系统中具有很好的应用前景。

评论