一种系统芯片的功能测试方法

3.2 功能测试平台的构建

本文引用地址:http://www.amcfsurvey.com/article/86637.htm从图1可以看出,“成电之芯”主要有以下几类接口:36位的输入信号总线Input,用来为芯片提供初始输入激励;32位的初始化数据总线Initial_bus,用来为芯片提供DSP核程序、控制寄存器参数、脉压系数和滤波系数;48位的片外缓存数据总线IQ1和IQ2,用于将脉冲压缩的结果传送到片外缓存;28位的求模或取对数输出总线Log_out,用于输出脉冲压缩或滤波运算后的求模或取对数结果;56位的滤波结果输出FIR_I_OUT(28位)、FIR_Q_OUT(28位),用于输出MTI或MTD处理后的结果;16位的HD数据总线,用于输出DSP核处理后的结果。

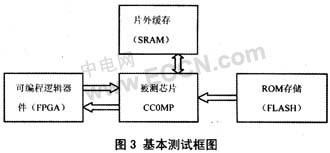

根据基于可编程器件建立测试平台的设计思想,功能测试平台的构建方法如下:采用可编程逻辑器件进行输入激励的产生和输出响应的处理;采用ROM来实现DSP核程序、控制寄存器参数、脉压系数和滤波系数的存储;采用SRAM作为片外缓存。基本测试框图如图3所示。

根据“成电之芯”的要求,芯片需要外部提供136 k 32bit的存储空间为其提供脉压系数和滤波系数,同时需要其它的一些存储空间为芯片存储片外的DSP核程序和控制寄存器。

由于做MTD滤波时,每个相参处理间隔的数据量最大为2M深度,所以片外必须准备两片深度为2M,数据宽度为48位的SRAM作为芯片的片外缓存。

除此之外,芯片需要外界输入数据和控制信号,并且需要接收芯片的输出数据。这部分的功能可通过可编程逻辑器件来完成。

通过以上分析,CCOMP芯片功能测试平台选用了两片SST39VF3201来做它的片外初始化存储器、6片GS832018来做它的片外缓存、一片XC3S5000来产生它的时序控制信号以及和外部接口的控制逻辑、两片MT48LC4M32用做它的输出缓存、两片SST39VF3201来做它的输入数据存储器,另外还选用了一个AD和一个DA芯片来实现与外界的数据通信。实现框图如图4所示。

4 测试平台的实现

4.1软件的实现

根据“成电之芯”输入激励和输出响应的数据对比要求,编写了可综合的verilog代码。代码的设计完全按照“成电之芯”的时序要求实现。

4.2 硬件的实现

根据功能测试平台的实现框图进行了原理图和PCB的设计,最后设计完成了一个可对“成电之芯”进行功能测试的系统平台。实物图如图5所示。

5 结论

本文通过对“成电之芯”功能测试平台的设计与实现,阐述了一种基于可编程逻辑器件的系统芯片功能测试平台的建立。本文从系统芯片的测试评估出发,一步步深入系统芯片测试方法分析,最终实现一个完整的测试平台。

该系统除了阐述功能测试平台的实现方法外,同时也对待测芯片——“成电之芯”进行了充分的测试,为每一块芯片的功能是否完好提供了重要依据。

评论