针对功率设计的SDR解决方案

由于像美国联合战术无线电系统(JTRS)这样的计划,软件定义的无线电(SDR)早已被证实。然而,有许多问题严重地制约着SDR的广泛部署,其中相当重要的问题就是功率。

本文引用地址:http://www.amcfsurvey.com/article/86635.htm功率是在设计每一个SDR子系统时的主要考虑因素,特别是因为它们要消耗比硬件无线电更多的功率。例如,为了获得预期的无线电通信距离(依赖于链路的状况,典型值为5-10千米数量级),射频(RF)前端必须具备足够的发射功率。同样,对于靠电池工作的无线电设备,RF前端、调制解调器和加密处理子系统的功耗都直接影响无线电设备的寿命。此外,对由调制解调器产生的热量进行散热的能力直接影响到无线电设备的寿命,并且甚至可能影响到能在机箱中同时处理的通道数,且有更多的影响。

因此,降低一个SDR的功率有许多好处,这些好处可能甚至包括通过购买更少的备用电池而降低运营费用。在此,为了获得其中的一些好处,我们谈论的重点将放在降低SDR调制解调器功耗的整体方法上。

降低功耗的硬件方法

为了降低调制解调器中的功耗,大多数人首先注意的就是在处理过程中的硬件,其中,通常包含现场可编程门阵列(FPGA)、数字信号处理器(DSP)和通用目的处理器(GPP)。区分任何硬件器件的两个功耗源——静态功耗和动态功耗——是至关重要的。静态功耗是一个已加电但不活跃的器件所消耗的固有功率,由晶体管的电流泄漏所控制。另一方面,动态功耗是由活跃使用的器件所消耗的功率,该功率受到若干变量的影响,包括电源电压、对外部存储器的访问次数、数据带宽,等等。检测两种类型的功耗是至关重要的,特别是在无线电设备具有一个通常接收比发射更长的占空周期的情形下。在GPP和甚至DSP的情形下,像频率调节、电压调节和电源关闭模式这样的电源管理功能已经变得日益普遍。然而,关于FPGA又是什么情况呢?

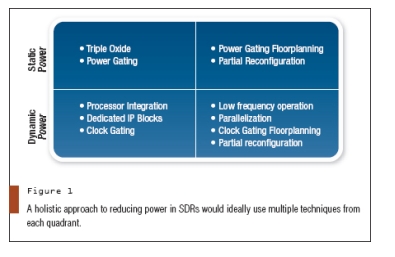

图1:用于降低SDR功耗的一种真正的整体方法要采用来自每一个象限的多种技术。

有许多方法可以用来降低FPGA中的静态或动态功耗,其中许多方法不是可以同时应用的。一些降低静态功耗的方法包括三极栅氧化层电源门控。

利用三极栅氧化层,硅供应商在晶体管上覆盖一层氧化层以减少泄漏;覆盖层越厚,泄漏就越小。性能保持平衡。在内核中需要性能的地方,常见的就是采用薄的氧化层;而对于驱动较高电压的I/O,要采用厚的氧化层。在不需要最大性能的地方,如配置SRAM,附加的中间氧化层可以极大地降低泄漏。利用这种技术的FPGA的例子包括赛灵思的Virtex-4和Virtex-5系列。

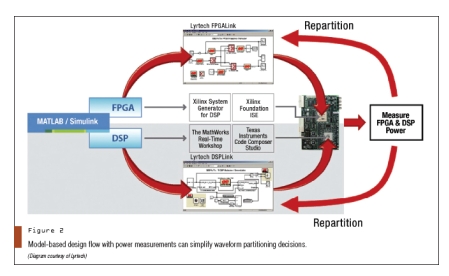

图2:带有功率测量值的基于模型设计流程可以简化对波形划分的决策。

当FPGA模块未被使用时,电源门控涉及晶体管的使用以降低待机泄漏。这种技术的一个例子可以在低功耗睡眠模式中看到。例如,如果在一个FPGA中的所有模块都被电源门控,该器件就消耗非常小的静态功耗。在这种情形下,平衡的是FPGA的配置的损耗,以便该器件在唤醒过程期间被完全地重配置,这个过程可能要花几毫秒。另一方面,除了那些具有配置的模块(比如配置存储器)之外,如果所有的模块都被电源门控,那么,FPGA的状态就被保持住了。尽管唤醒时间被极大地缩短了,但是,所节省的功率远远不如当所有模块都被电源门控时那样显著。赛灵思的Spartan-3A系列的FPGA支持两种类型的电源门控。

动态功耗是功率等式的另外一部分。降低动态功耗的方法包括处理器集成、专用IP模块和时钟门控。

对于具有嵌入式GPP和DSP引擎的平台FPGA来说,处理器集成是非常有用的。通过采用嵌入式GPP,而不是离散的GPP,就不必驱动数据从FPGA跨越外部I/O线到GPP(跨越外部I/O线通常消耗大量的功率),从而节省功率。Virtex-4 FX器件就是平台FPGA的一个例子。

让专用IP模块来执行某些常见的函数可以极大地降低动态功耗而对灵活性却没有重大影响。一个例子就是让FPGA中的专用引擎执行乘法——累加函数。与采用逻辑电路实现的方案相比,这种专用IP模块能够以高得多的性能执行那个函数并省电85%以上。Virtex-5器件具有包括DSP引擎、Ethernet MAC和PCI Express端点在内的许多专用模块,使得其可以以较低的功耗提供先进的功能。

时钟门控技术采用电路来关闭不用的FPGA模块的时钟,因而把那些模块的功耗降低到泄漏电流的数量。如Virtex-4和Virtex-5这样的FPGA就是支持这种性能的最好范例。

因为降低静态和动态功耗都是至关重要的,从硬件对两者的影响来看,最强有力的方法就是进一步降低电源电压。最佳的例子之一就是进一步降低内核电压。处理器件随着它们向下一代工艺节点转移(也就是从90nm向65nm转移)而趋向受益于较低的电压。例如,65nm Virtex-5 FPGA的内核电压是1.0V,比工作于1.2V的90nm Virtex-4 FPGA低17%,比工作于1.5V的130nm Virtex-II FPGA低33%。这就是采用大多数当前器件的好处之一。较低的内核电压对静态和动态功耗两者都有重大影响,因为泄漏与电压呈指数关系,而动态功耗与电压呈二次方的关系。因此,Virtex-5器件比Virtex-4 FPGA的静态和动态功耗平均低30%以上。

上面我们讨论了降低SDR中功耗的若干硬件方法,这些方法都重要,但是,感觉像缺少了一些内容。毕竟,这不是被称为软件定义的无线电吗?尽管设计工程师愿意对硬件提供商谈关于降低它们的器件功耗的问题,但是,现实是许多所谓的“硬件公司”拥有的软件工程师比硬件工程师要多。确实,这似乎预示着降低功耗不仅仅是硬件的事情。

评论