仿真扩展芯片(EEC)简化高速汽车嵌入式处理器的集成

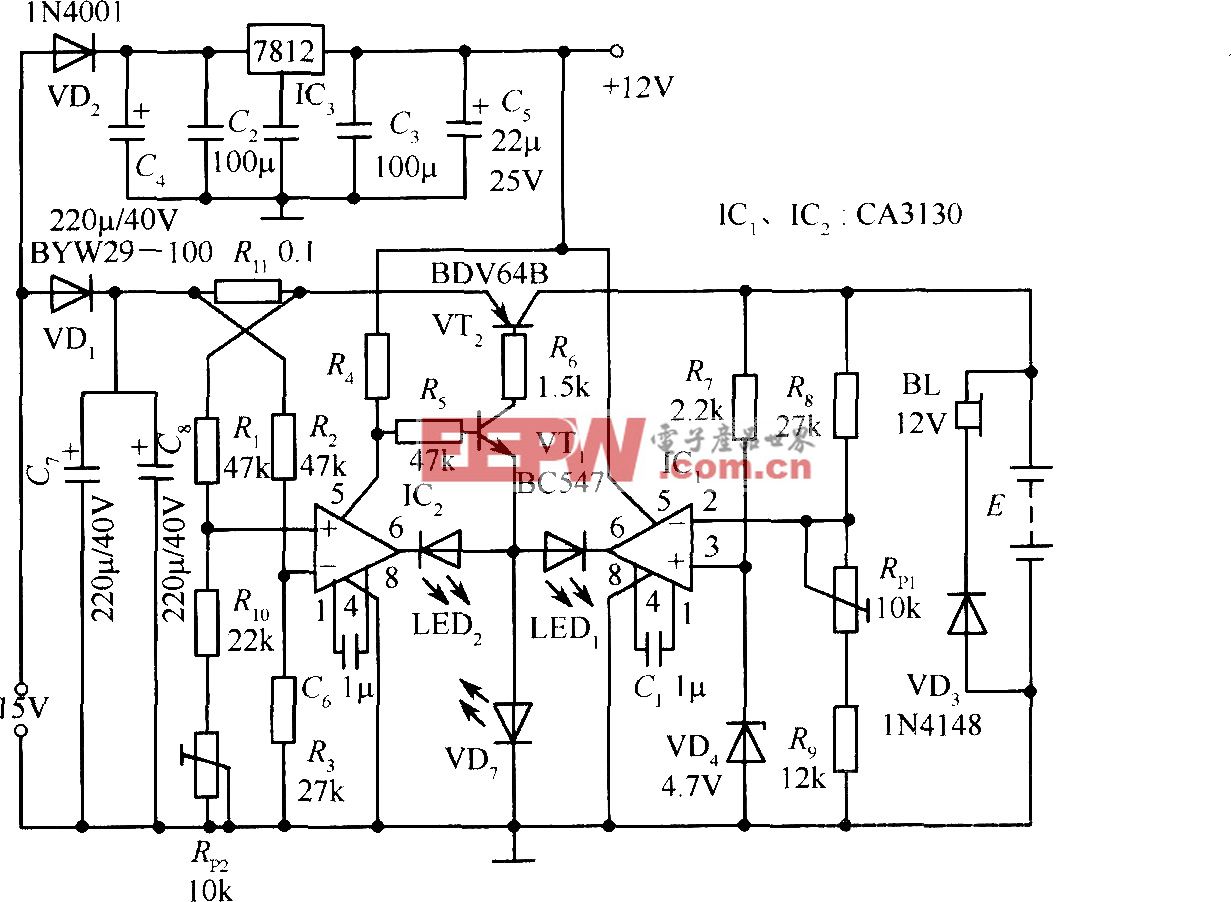

仿真设备使用一个原始生产器件的宏指令,完成所有的一般性功能、外设及端口,接着在外缘添加一个512K的静态随机存取存储器(SRAM)、几个总线观察模块(BOB)及一个拥有一些本地存储器来控制仿真器的局部CPU(在此情况下为另一PCP 2)。若干高速串口,包括USB、JTAG和Micro- Link端口提供了外部连接口。该附加的线路,也叫EEC(仿真扩展芯片),在大规模生产器件发生改变时,使得仿真器很容易被重新设计,因为互连点并没有发生变化。

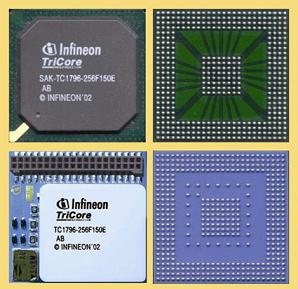

本文引用地址:http://www.amcfsurvey.com/article/85220.htm传统的外绑器件的另一常见问题在于封装的大小。仿真设备被特别设计成与标准的生产器件占位面积相符合,并且拥有一组额外添加的针脚来提供更多的信号。同时,还给封装直接添加了一个顶端连接,通过可移动的连接器就可以采集相同的信号,下方图象分别显示了大规模生产器件封装(顶端)及仿真设备封装(底端)。

仿真设备甚至提供了比传统的ICE更多的性能,这些性能包括:

跟踪性能:

TriCore程序、数据及状况跟踪;

PCP程序、数据及线路跟踪;

所有控制多个组件的主线全方位的可视性;

缓冲器跟踪数据的优化压缩;

所有的跟踪在时间上都全面地得到校正;

中央时标单元;

事件前后跟踪缓冲(逻辑分析仪)

触发逻辑性能:

触发器能够用于触发中断、跟踪限制及开始/停止跟踪;

用于控制指令时针及数据地址的范围比较器;

用于控制数据掩模对等/范围比较器;

附加的外部事件输入(2)及输出(4);

用于计算事件、并在计算和时间基础上进行时间测量及事件生成的计数器;

同时地、有选择性地开始和停止所有内核存储器的中央机制;

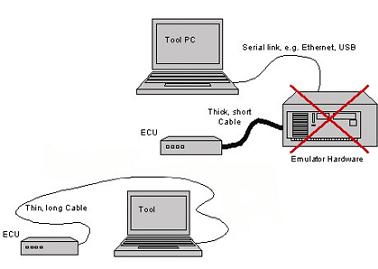

仿真器同时也提供了特殊的重启模式,通过各种重启进行调试和校准,开机重启除外(见下图)。

仿真设备将仿真器功能嵌入目标应用的生产器件封装中,因此,外置仿真器硬件不再为人们所需。

EEC中512Kb SRAM是由许多能够配置的零碎存储空间组合而成的,这些零碎的存储空间能够被任意指派不同的任务。这使单一器件能够使用于不同的应用情况中。这些功能包括:

—逻辑分析仪模式:SRAM用于(与压缩规则系统同时)跟踪任一内部总线及内核存储器的程序及数据流程。

—软件开发模式:SRAM用于存储程序代码,避免改变时产生老化的闪存,同时允许无限的基于软件之上的断点的存在。

—校正标定:SRAM用于暂时存储所需的校正常量。当发生存取时,校正标定硬件将取数方向由内部闪存转变为EEC SRAM。外置校正工具能够通过USB接口或JTAG接口来对SRAM的零碎存储空间进行快速灵活的读写。

—快速制作原型:SRAM作为外置快速原型硬件和微控制器之间的消息缓冲器。由于延迟时间要求低于3ms,USB接口不适于此项任务,因此可以使用MicroLink端口或JTAG接口(延迟时间约为2us,带宽约为3Mbps)。

—“飞行”记录仪:SRAM用于记录系统中使用的数据,或用于跟踪发生特定错误时系统的情况。

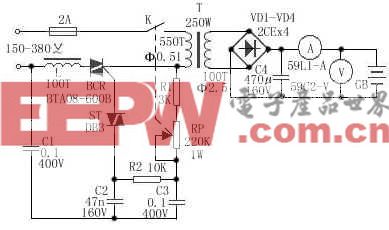

仿真设备是由主机PC在运行时配置而成的,该接口受到严格的规定,因此各种软件工具能够基于同一标准进行互操作。NEXUS并行的、基于总线的跟踪端口在此不能直接应用,因此只能重新使用软件编程接口(API)。支持仿真概念的软件提供了一个器件存取服务器(DAS)。该接口允许多个工具例程装于一台PC 中,以共享与嵌入式主机(USB、JPAG)相连的单一通信路径。DAS同样允许多个处理器例程与内置的嵌入式主机相连。因此,在将来,也可以访问更大规模的系统级芯片器件。DAS也支持外在控制协议(XPC)标准,该协议使校准和记录工具能够与物理连接媒介独立地连接起来(CAN、FlexRay、 USB、JTAG)。

由于时钟速度的加快,高度集成的系统级芯片微控制器的调试和校准只会变得更加的困难。使用一个嵌入式仿真设备能够为软件工程师们提供微控制器内部工作情况的可视性,确保系统软件在现实世界任何条件下都有正确而强大的功能。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论