仿真扩展芯片(EEC)简化高速汽车嵌入式处理器的集成

由于微控制器时钟速度的加快,调试和校准变得更加地困难。嵌入式仿真设备能够为汽车电子设计工程师提供高度集成的系统级芯片(SoC)微控制器内部的可视性。

本文引用地址:http://www.amcfsurvey.com/article/85220.htm自动代码生成工具能够通过基于图示模型之上的设计生成C代码。对该工具越来越多的使用可以节省软件工程投入的时间,但同时也给软件工程文化带来巨大的变化。

软件工程师将现有的模块组合在一起,建立成一个系统,并对该系统作出检测。与把定制的模块写入一个系统中以满足系统要求的方法相比,该方法的效率更高。对该通用的模块化软件的再利用提高了开发效率和软件质量。但同样也导致结构松散,存储器效率低下,长时间的延迟及将设计过程从硬件中抽象出来。

在不改变基本软件的情况下,这些系统的性能能够转变成不同版本的机械硬件。一般情况下,这是通过将许多校准了的变量包括在内而实现的,因此才能够在运行期间使能或禁止功能,调整增益,同时在运行时改变查找表。

软件工程师依靠仿真技术来跟踪真实系统中的程序流程,关注随时更新的数据,测量延迟,并且排除逻辑错误。但是,在为这些系统除错时,由于时钟速度过高,给多内核存储器系统级芯片的集成带来了一些挑战。

设计障碍

嵌入式非易失存储器的体积持续增大,硅片的几何形状持续缩小,使得规模大的系统级芯片微控制器能够与应用广泛的高速内部总线连接在一起,并通过这些总线将信息反馈给多个具有高速缓冲存储器的流水线型内核存储处理器及协调处理器。该体系同样能够使微控制器子系统能够被集成到更深层次的应用环境。由于存在物理连接问题(有时甚至连一根外部总线都没有),以及时钟速度过高、电缆长度及环境温度等因素,将分析设备集成到深度嵌入式器件的外部总线上的难度很大。

在许多情况下,可通过外部总线察看的外部取数情况并不代表整个程序的流程,因为内部高速缓冲存储器及流水线能够对取数做出预测。突发模式闪存同样由于假定的连续地址增量使得所获得的数据的解码变得更加复杂。

连接仿真系统时的首要问题在于连接长度受到限制,因为系统时钟的速度过高。例如,如果使用一个频率为150MHz的微控制器,那么,50cm长的连接线造成的传输时间延迟大约为2.0ns,但是时钟周期仅为6.67ns,所以2.0ns的单向延误时间是相当巨大的。由于在这些高频率器件中,连接线扮演着传输线的角色,并且它们的终接阻抗是无法得到保障的,因此,这看似短暂的时间几乎妨碍了任何远离目标器件的控制功能。在这个例子中,想要忽略传输线造成的时间上的延迟,线路的最大长度不能超过16cm。所以,在线仿真器(ICE)具有与被测发动机电控单(ECU)相同的环境需求。

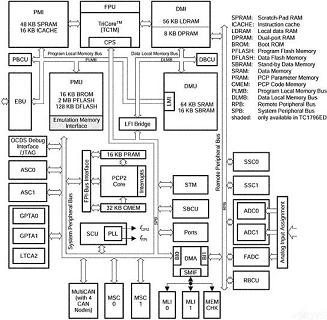

Ingineon公司的TC1796产品即为此类系统级芯片实现的一个很好的例子。32位的TriCore中央处理器(CPU)拥有代码和数据分别独立的总线,并且通过LFI与系统总线桥接起来,建立起一个与外设子系统相连的数据通道。此外,还有一个通过直接存储器存取(DMA)与远端外设总线相连的通道。

外设控制处理器(PCP2)也是一个32位的CPU。同样的,该处理器也有独立的通常无法看见的数据和程序总线。该处理器的子系统的最高频率为 150MHz,外设子系统最高频率为75MHz,因此,它有两个时钟区域。该器件被封装于一个416引脚的球型格栅极阵列封装中,能够提供标准的JTAG 除错接口以支持除错功能。但是,要完全仿真这样一个微控制器,需要能够检验与外部针脚不相连的许多不同内部总线之间的数据交换。巨大的嵌入式存储器 (2Mb闪存)有广泛的内部取数路径(128位)和局部高速缓冲存储器。因此,内置存储器的执行比外置(32位存取)存储器快得多(见下方TC1796方框图)。

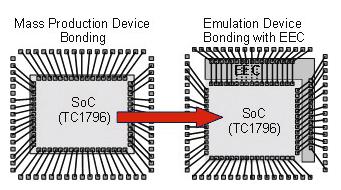

多总线及多内核存储器的复杂性意味着,只有一个外绑器件(现场可编程门阵列, FAPG)才能够达到完全除去系统错误所需的可视度水平。但是,如前面所讨论的,频率为150MHz的总线周期仅为6.67ns,一个外置的外绑控制器在这段时间内要接收总线信息,并对其解码,还要决定需要触发的中断及暂停处理器,因此,给予控制器的时间是远远不够的。在这种情况下,解决问题的方法就是将仿真器安装于外绑器件中,形成所谓的仿真设备(见下方对比图:左方为大规模生产器件,右方为拥有仿真扩展芯片的仿真设备)。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论