基于FPGA的核物理实验定标器的设计与实现

定标器在大学实验中有很广泛的应用,其中近代物理实验中的核物理实验里就有2个实验(G-M计数管和β吸收)要用到高压电源和定标器,而目前现有的设备一般使用的是分立元器件,已严重老化,高压极不稳定,维护也较为困难;另一方面在许多常用功能上明显欠缺,使得学生的实验课难以维持。为此我们提出了一种新的设计方案:采用EDA进行结构设计,充分发挥FPGA(Field Programmable Gate Array)技术的集成特性,抛弃原电路中众多晶体管,成功地对系统中的大量处理电路进行了简化和集约,提高了仪器的可靠性和稳定性,有利于电路的测试和检修。改进方案后的定标器不仅完善了原有的功能,还增加了数据存储、RS232接口等功能,可以方便地与PC机接口通信,进行数据处理、图像显示和打印等。

本文引用地址:http://www.amcfsurvey.com/article/85071.htm1 G-M计数器原理

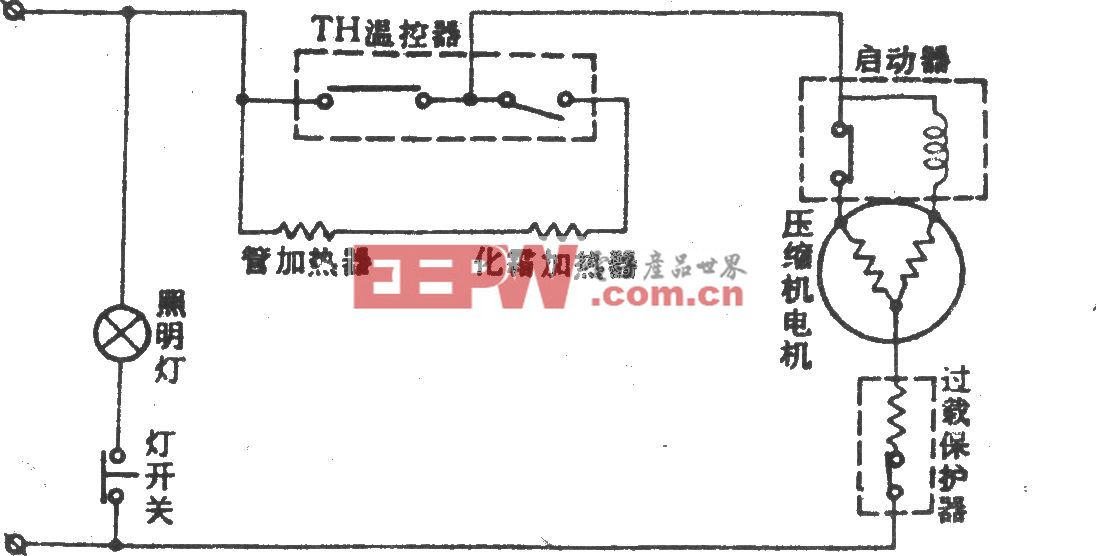

G-M计数管是一种低压气体放电管,作用是将入射粒子(射线)转换成电压脉冲输出。原子核心物理实验中常用它作为计数装置的“探头”探测射线及射线强度。G-M计数管有2种:用于探测β射线的钟罩型和主要用于探测γ射线的长圆柱型。其中钟罩型β计数管的工作电压为千V(伏)左右,圆柱型工作电压接近千V(伏)。

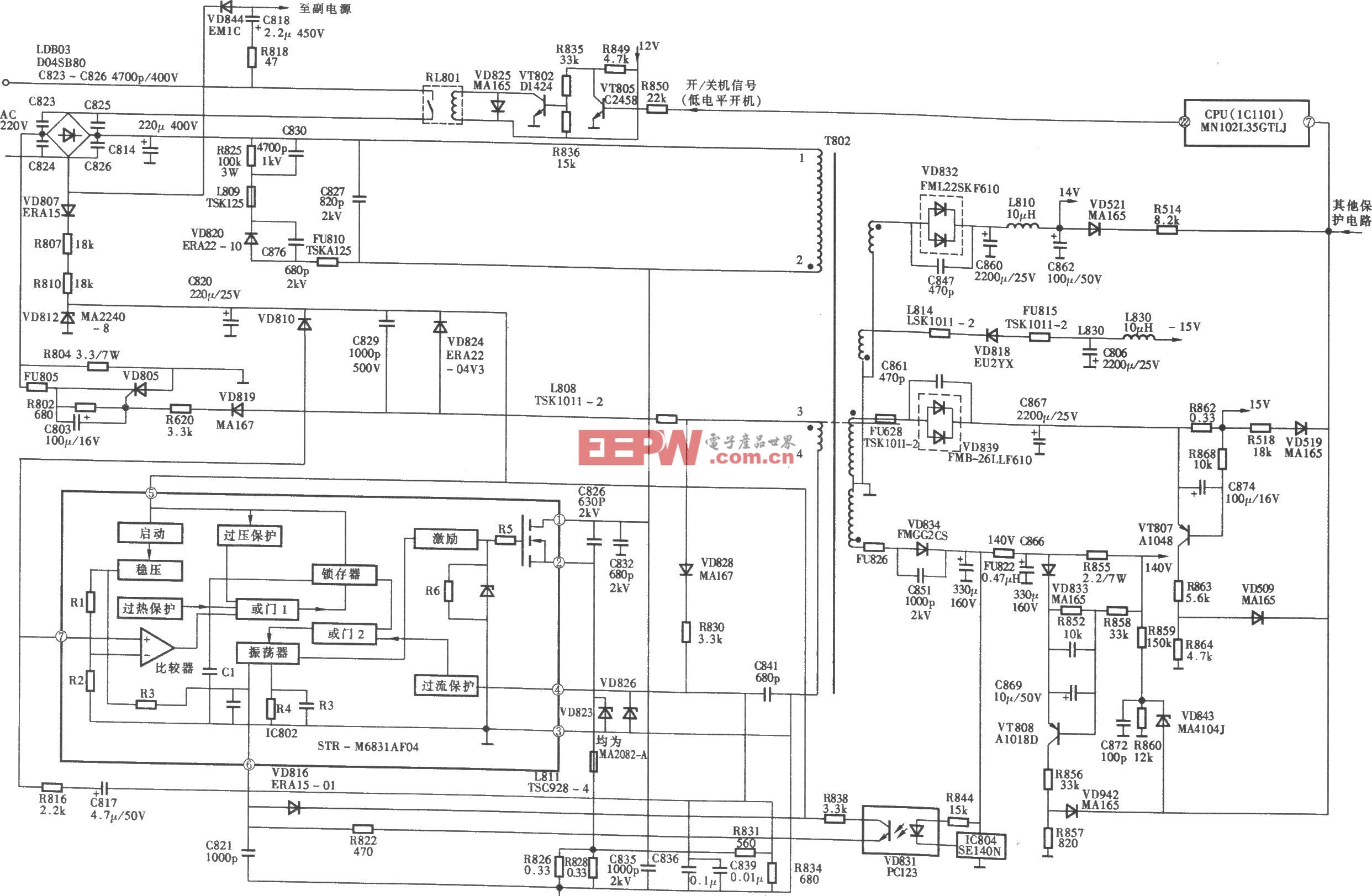

射线粒子在计数管中引起气体“雪崩”放电,使得计数管导通;电流通过负载电阻R形成一个负脉冲,此脉冲信号通过电容C,经前置放大器送至定标器计数,如图1所示。由于计数管在放电终止后会形成连续放电现象,此现对计数管极其有害,故一发现计数突然增加时,就应立即降低高压。改进后的定标器会自动控制高压源,将其电压降低。这些改进。即可避免以前实验中出现的计数管损坏问题。

2 定标系统原理及硬件实现

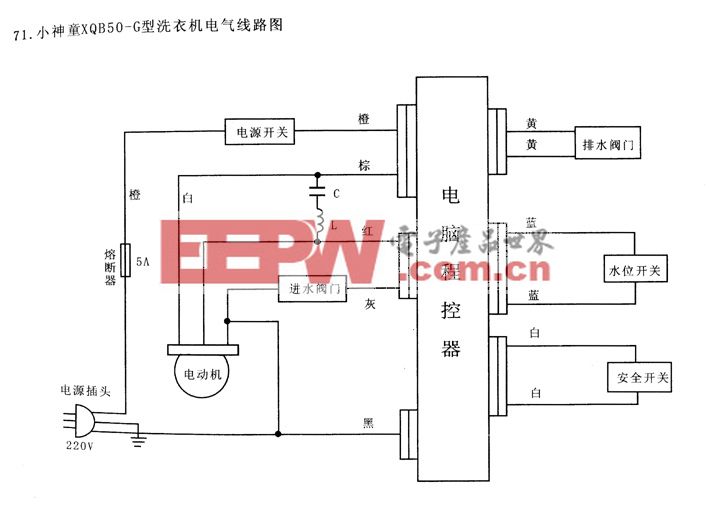

定标器系统由电源部分、输入电路部分和脉冲计数显示部分3个模块组成,原理框图如图2所示。

G-M计数管产生的负脉冲经过输入整形电路,进行整形、放大处理,产生标准TTL信号,再由计数测量电路进行计数。定时脉宽门控电路控制计数的脉宽,分6个档:×10 -3、×10 -2、×10 -1、×10 0、×10 1、×10 2。时间倍乘档有4种选择:×1、×2、×4、×8。这样进行的一组测量数据即可以用来描述射线粒子产生的规律。 图2中,显示部分采用的是动态显示的方法,利用单片机AT89C51来进行即时的控制和相应的显示数据。同时根据需要,选择部分测量数据(包括此次计数数据及对应的高压值)存储到RAM中,然后将所选取的RAM中的数据通过RS232串行端口发送到PC机上,经过相应的处理软件进行描图,以及相应的实验数据处理。为了使系统更加集成化,特定时脉宽门控、计数测量电路、地址译码及数据锁存、总线的驱动等电路集成到1片FLEX10K的FPGA中。图3为系统详细电路原理框图。

3 FPGA芯片设计

3.1 FPGA逻辑功能结构及其总体设计

为了简化设计,实现系统大量逻辑电路的集成,在设计中使用了现场可编程逻辑门阵列器件(FPGA)。FPGA主要实现以下逻辑功能:定时脉宽门控、计数测量、地址锁存、译码、总线的驱动和扩展以及数码显示的控制等功能。其逻辑功能顶层结构如图4所示。FPGA器件选择Altera公司FLEX10K10系列的EPF10K10LC84-4芯片。该芯片集成有1万个等效逻辑门,含有572个逻辑单元(LEs)、72个逻辑阵列块(LABs)、3个嵌入式阵列块(EAB s),并具有720个片内寄存器,可以在不占用内部资源的条件下实现6144 bit的片内存储器;内部模块间采用高速、延时可预测的快速通道连接;逻辑单元间具有高速、高扇出的级联链和快速进位链;片内还有三态网络和6个全局时钟、4个全局清零信号以及丰富的I/O资源;每个I/O引脚可以选择为三态控制或集电极开路输出,可以通过编程控制每个I/O引脚的速度以及I/O寄存器的使用。

FPGA使用的开发软件为MAX+PLUS II。该软件是一个集设计输入、编译、仿真和编程为一体的超级集成环境;提供了自动逻辑综合工具,可以在多个逻辑层次上对高级设计描述进行综合、优化,大大缩短了编译时间,加速了FPGA设计开发进程。MAX+PLUS II支持各种HDL输入选项,包括VHDL、Verilog HDL和ALTERA的硬件描述语言AHDL;提供丰富的库单元供设计者调用,其中包括74个系列的全部器件和多种特殊的逻辑宏单元(macrofunction),以及新型的参数化的巨单元(magafunction)。

评论