基于FPGA的数字式光端机的研究与设计

4 并串/串并模块

本文引用地址:http://www.amcfsurvey.com/article/83485.htm低压差分信号是由ANSI/TIA/EIA-644-1995定义的用于高速数据传输的物理层接口标准(LVDS)。它具有超高速(速率可达1.4Gb/s)、超低功耗和低电磁辐射等特性,因而是在铜介质上实现千兆位速率通信的优选方案。而总线形低压差分信号LVDS是LVDS技术在多点通信领域的扩展,它要求有更大的驱动电流(10mA)和更好的阻抗匹配设计。

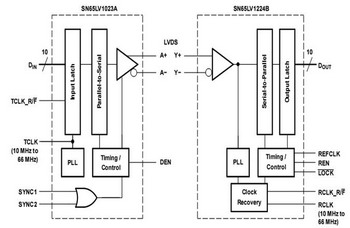

SN65LV1023和SN65LV1224是TI公司推出的10位总线型低压差分信号的应用芯片组。其中SN65LV1023是可将10位并行CMOS或TTL数据转换为具有内嵌时钟的高速串行差分数据流的串化器;而SN65LV1224则是接收该差分数据流并将它们转换为并行数据的解串器,它同时又可以重建并行时钟。采用该器件组进行数据串化时采用的是内嵌时钟,这样可有效地解决由于时钟与数据的不严格同步而制约高速传输的瓶颈问题。此处的硬件电路设计如图4所示。

图4 并串转化硬件示意图

系统软件设计

系统软件主要是对系统控制核心的FPGA的编程。整个程序基于模块化、结构化的软件开发思想编写。所用的开发工具是Altera公司出品的FPGA集成开发环境QuartusII,开发语言采用当今比较流行的大规模集成电路Verilog开发语言。

系统软件功能实现了A/D控制模块、语音编码控制模块、并串转换控制模块、串并转换控制模块、D/A控制模块、语音解码控制模块和反向数据的收发控制模块。

1 A/D控制模块

A/D控制模块以FPGA为主控核心,为AD9280提供采样时钟;同时采集AD9280A/D转换后的数字量。

FPGA系统时钟频率为32MHz,对于AD9280的采样时钟为16MHz,对系统时钟进行二分频后提供给AD9280。同时,在分频后的输出时钟的上升沿对A/D转换的结果进行读取,读取的结果存入FPGA中进行下一步应用。程序如下所示。

module PcmControl(clk_in,reset,tdd,tdc,tde,pcm_data);

……

always@(posedge clk_in)

begin

if(reset)

begintdc<=0; end

elsebegin

if(cnt0==7)

begin

tdc<=~tdc;

cnt0<=0;

end

else

cnt0<=cnt0+1;

end

end

always@(posedge tdc)

begin

if(cnt1==140)

begin

tde<=~tde;

cnt1<=0;

end

else

cnt1<=cnt1+1;

end

always@(posedge tdc)

begin

pcm_data<=tdd;

end

endmodule

其中,clk_in是FPGA系统时钟,reset为系统复位信号。信号tdd是PCM编码芯片的输出;信号pcm_data用来存放PCM编码数据;信号tdc是PCM编码时钟信号;信号tde是PCM编码使能时钟。

fpga相关文章:fpga是什么

评论