AD9857在DVB-T调制器系统中的应用

欧洲提出的数字视频地面广播(DVB-T)采用编码正交频分复用COFDM(Coded Orthogonal Frequency Division Multiplexing) ,即:DVB-T COFDM。COFDM系统可以有效提高频谱利用率,在时间扩散环境中尽可能抑制因多径传输而产生的符号间干扰和码间干扰。选择DVB-T标准的国家除英国、法国、西班牙、瑞典等欧洲国家外,还有澳大利亚、新西兰、新加坡、印度等国家和地区。

本文引用地址:http://www.amcfsurvey.com/article/83484.htm本文基于DVB-T标准设计并实现了一个COFDM调制器。设计中,使用了Altera公司的Stratix系列EP1S25F672C7的FPGA和Analog Devices公司的数字正交上变频器AD9857。本系统设计简单,工作稳定,输出信号的信噪比可以达到55dB以上,能够以较低的复杂度得到较高的系统性能。

1 DVB-T调制器的系统方案

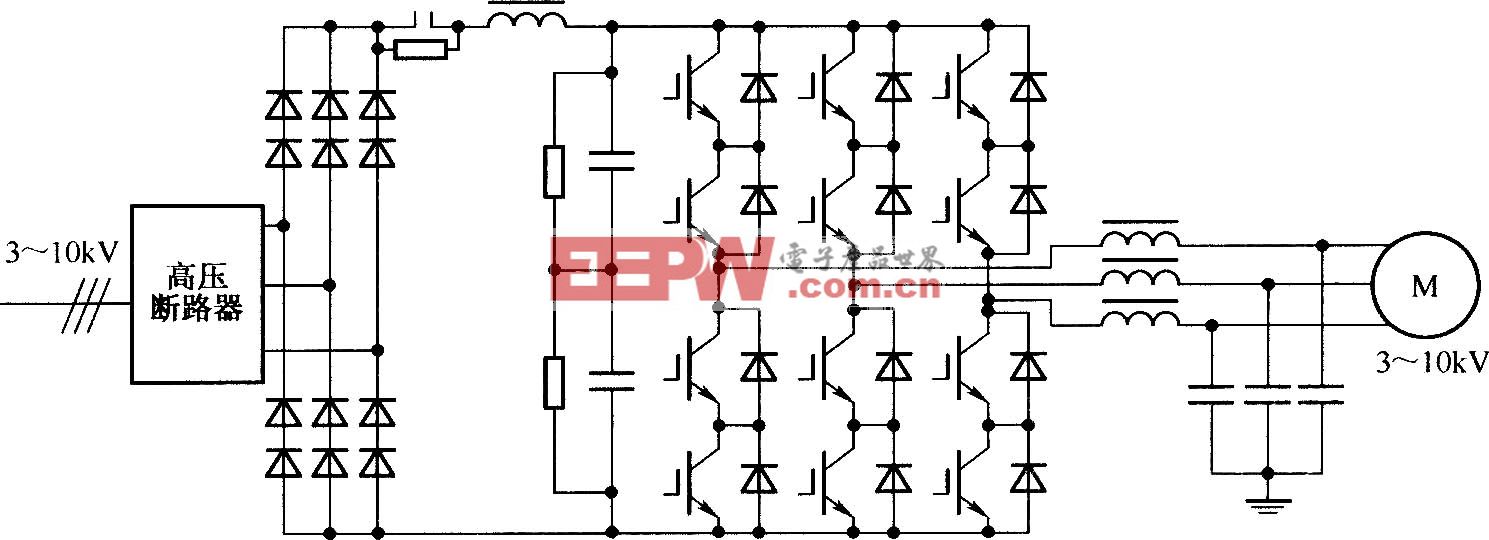

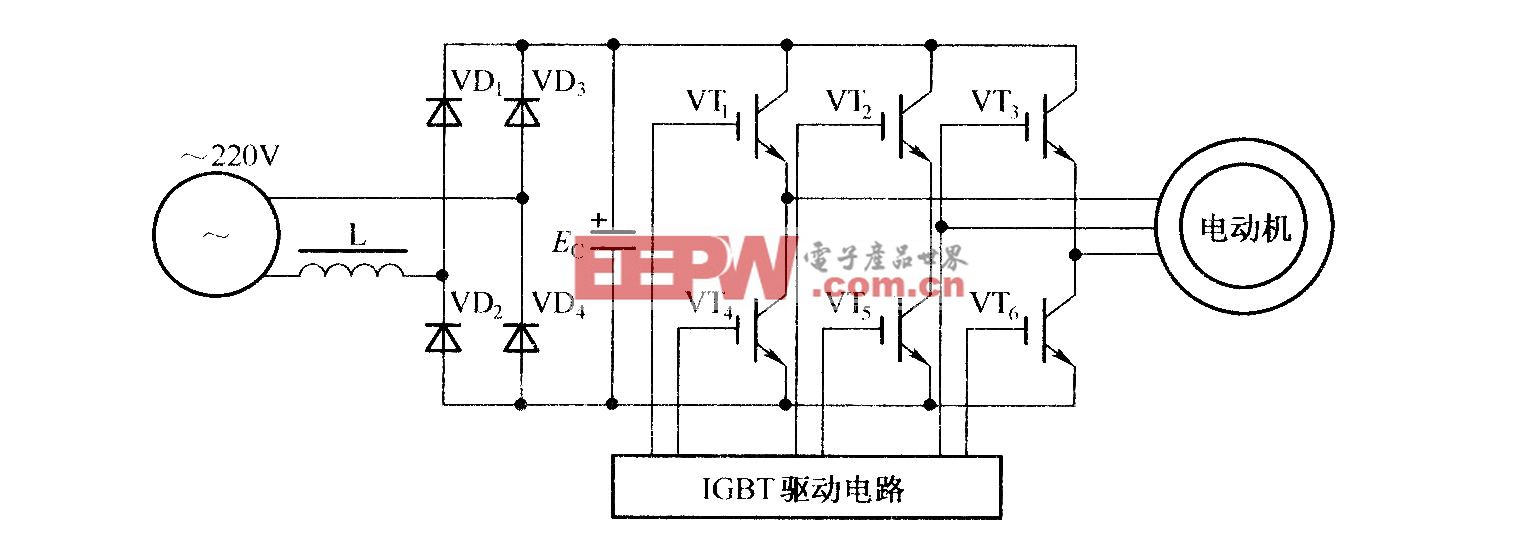

DVB-T调制器中COFDM调制系统是调制器中的主要部分,也是抗多径的OFDM技术在宽带无线通信中一个很好的利用。调制系统框图如图1所示。

从图中可以看出,发射端首先由信源去复用电路将输入的TS码流分解成两个独立的连续数据流,每188字节为一个传输包;然后对每一路数据进行加扰、RS编码、外交织、卷积编码,在去复用电路中将两路合二为一(一般分层模式下用到两路流,其它模式只对一路去复用),再经比特交织器和符号交织器完成整个信道编码。编码后数据经过映射调制到对应的星座图上成为数据载波。OFDM帧形成部分将数据载波、导频载波(pilot)和TPS信道传输参数信令载波按照帧结构的要求组合在一起,形成完整的OFDM符号和帧。根据OFDM调制原理,将各个载波经过IFFT变换得到时域的数据流。之后,在每个OFDM符号前插入保护间隔,再经过D/A上变频最终形成中频信号发射到信道中去。

可见,一个COFDM调制器主要由TS码流接入、信道编码调制和D/A上变频这三个模块组成。因此,D/A上变频的好坏,直接影响调制器的性能。

2 D/A上变频的原理

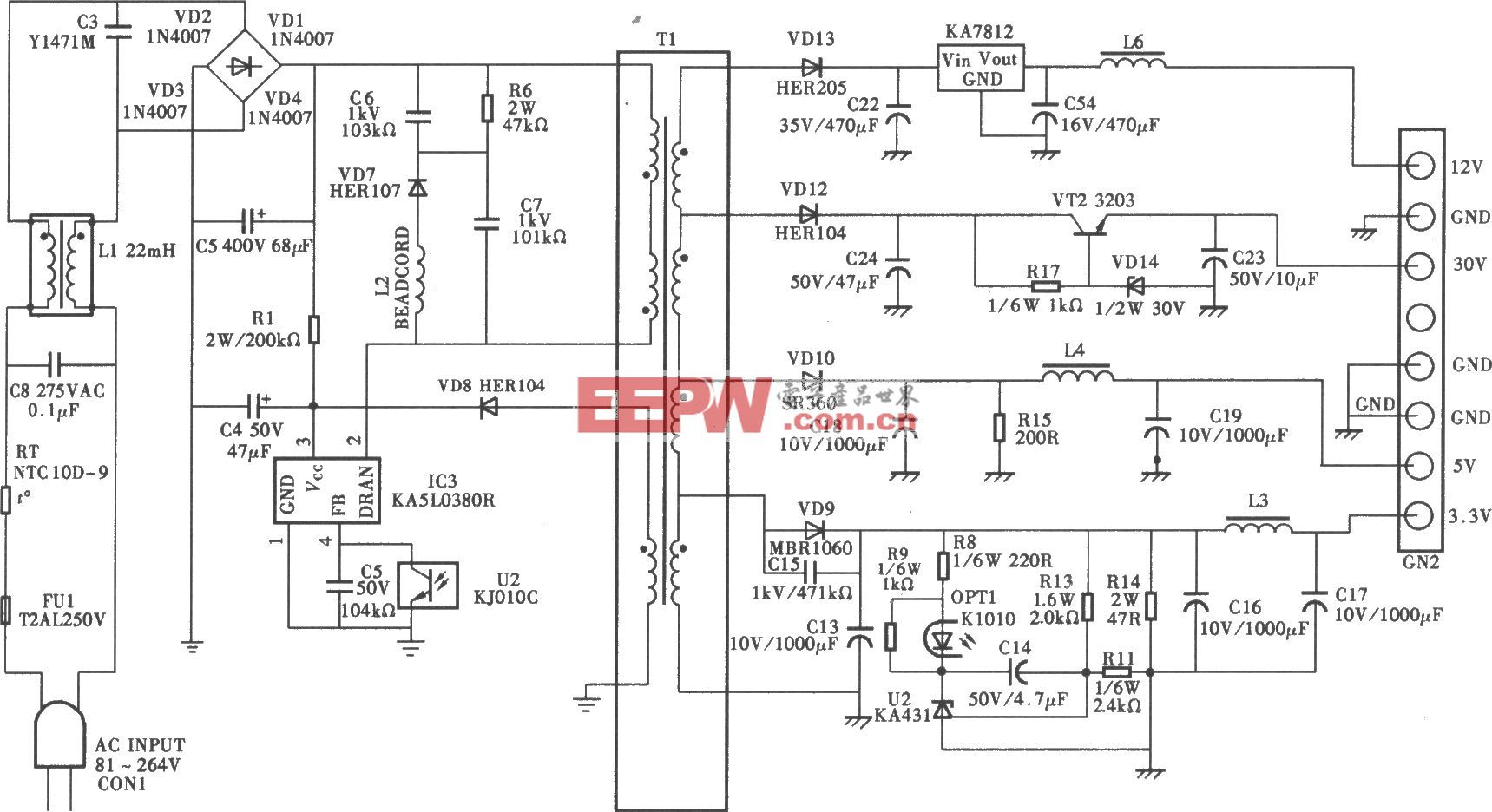

一般调制器的上变频可以采用模拟方式和数字方式两种方案,图2为一简单模拟上变频的实现电路,它的原理就是利用压控振荡器的振荡频率来实现调频。首先,输入信号经过VCO与本振信号混频后得到和频与差频信号;这些信号经过高通滤波器以后,滤除掉低频分量,高频分量就可以经过放大器传输到信道中去。由于模拟电路的一些固有缺陷,例如抗干扰能力较差,精度较低等,所以这种上变频实现方法的稳定性和可靠性都较差。

随着高速器件和软件无线电技术的发展,数字上变频技术逐渐突破了模拟上变频的不足,具有调制中心频率可调、频偏可编程、调制方式可重组、调制码速率高、可实现较高的频响、可以与编码器合并扩展功能很强等优点,成为今后调制器的发展主流。

目前常用的数字上变频芯片是AD9856和AD9857,这两个芯片都是由AD公司生产的通用、高性能的数字上变频器件,具有集成度高、性能好、功耗低等特点,使用这两个芯片可以很容易实现信号的数字正交调制。AD9857与AD9856相比,还有如下的不同点:

(1)AD9857集成的是一个14bit的D/A转换器,而AD9856集成的则是一个12bit的D/A转换器,这样在数据的精度上,AD9857比AD9856高了大约6dB。

(2)AD9856需要3V电压供电,而一般的微控制器的工作电压是3.3V或5V,这样就需要一个电压转换芯片来进行电平适配。AD9857的工作电压是3.3V,可以与其他芯片共用一个电源。

(3)由于AD9857配置完成以后会产生一个PDCLK信号,而AD9856并不能返回这样一个信号,因此送入AD9857调制的I/Q两路信号的平衡性比AD9856要好,这样可以防止在进行OFDM调制时出现载波丢失现象。

(4)AD9857还具有输出电平控制功能,可以根据接收机的需要,动态的调节输出信号的电平。

鉴于AD9857的优点,以及DVB-T系统的具体需要,本文讨论了一种基于AD9857的数字上变频的实现方法。

3 AD9857工作原理

AD9857主要有三种工作模式:正交调制模式、单频输出模式和插值DAC模式。三种工作模式的选择是通过对控制寄存器的编程来实现的,在本系统中使用的是正交调制模式。

在正交调制模式下,AD9857通过管脚PDCLK/FUD对数据输入端提供一路同步时钟,用于同步I/Q两路数据的输入。I/Q两路数据共用14bit 的数据线,所以PDCLK 的时钟频率应该是单独的I 路或Q路数据速率的2倍,I/Q数据分时送入片内的DEMUX解复用为并行的I/Q两路数据,它们将依次经过两个插值滤波器。经滤波后, I/Q 数据分别与两个正交的余弦函数相乘后再相加(或相减)为一路信号。因为DAC 使用零阶保持采样, 所以信号在进行D/A转换前需要经过一个反SINC补偿的模块,以上过程均发生在数字域,最后数字中频信号送入DAC进行数模变换产生两路差分的模拟信号输出。

AD9857内部集成了一个数字直接频率合成器(DDS)用来产生数字的正、余弦波作为载波。DDS的32位频率控制字(FTWORD)通过同步串行口进行配置。AD9857内部共有4组寄存器,每一组都可存储32位频率字,这种特性允许输出载波频率根据需要灵活及时地改变。通常,要使一个高质量的振荡器具有100M~200MHz 的频率动态范围是非常困难的, 而AD9857 则允许使用一个较低频率的振荡器, 它可以将其内部的参考时钟通过倍频来产生SYSCLK,通过公式fout=(FTWORD×SYSCLK)/232就可以把基带信号调制成任意频率的中频信号。

评论