基于FPGA的PCB测试机硬件电路设计

FPGA 程序框架

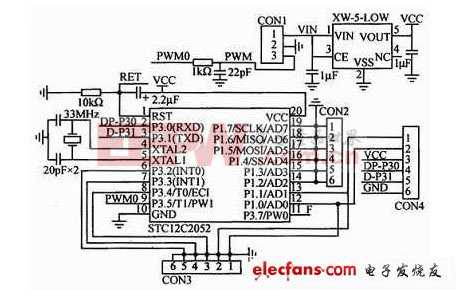

本文引用地址:http://www.amcfsurvey.com/article/83209.htmFPGA 片内程序是整个测试系统正确运行的关键。 由自顶向下的FPGA 设计原则,将系统分为5个独立的模块, 即通信模块(ISA) 、测试模块(TEST) 、AD/DA 模块、解码模块(DECODER) 、RAM 控制模块(RAMCTL)。

ISA 模块:系统通信及控制模块,完成与上位机通信、命令字解释、控制信号的产生等。系统根据上位机传送的导通电阻、绝缘电压等参数启动ADDA模块完成参考电压的输出;根据测试命令启动测试模块完成测试过程。数据在多个同步运行的同步状态机间传送,较难控制的是多进程间的数据通信与数据同步。

RAM控制模块:在测试开始前,上位机将测试点的信息通过总线传送至ISA模块, ISA 模块再将其存放到片内RAM中;测试完成后,将RAM中的测试结果传送到上位机。 在测试时测试模块通过读RAM中测试点的信息来打开相应测试开关,再将测试结果保存到RAM 中。 这样两个模块都要求读写RAM 以实现两个模块之间的数据共享,这就要求有一控制信号将两组读写信号线分别与RAM模块相连接,RAM控制模块即完成此功能。测试模块(TEST):虽然测试过程有多种,如开关卡自检、导通测试、绝缘测试等,但测试过程却是相同的,即测试扫描。 测试的工作过程是:加比较电路参考电压→打开待测点开关→延时→读比较器结果→测试另一组测试点。 本模块是按照不同的操作码,进入不同的测试过程。 测试结果与测试点编号一起组成13 位数据保存到RAM 中,并将原来测试点的编号信息覆盖。

解码模块(DECODER):这一模块挂在测试模块(TEST) 之后,它完成开关编号到实际电路的映射。 由于测试针阵形式不同、译码电路与控制电路的硬件设计不同,上级模块输出的测试开关信息并不能直接作为输出控制测试开关电路。 解码模块完成这两者间的转换。

AD/DA 模块(AD/DA):设计SPI 总线接口对A/D 及D/A 器件操作,模块以允许(adenable , daenable) 信号启动,以busy信号作为转换完成标志信号,将A/D及D/A操作相对其它模块进行封装。系统的每个模块采用Verilog硬件描述语言编写,采用多个多层嵌套的同步状态机(FSM)完成整个系统的逻辑功能;每一模块应用仿真工具Modelsim完成模块的功能仿真,系统完成功能测试后;利用Altera 综合布线工具QuartusII完成系统后仿真及综合、布线、下载;充分利用Altera公司免费提供的IPcore 对程序模块进行优化;顶层设计采用方框图输入方式,模块间的数据流由方框图更直观地表现出来。

结束语

基于FPGA的PCB测试机的硬件控制系统,提高了PCB测试机的测试速度、简化电路的设计。此外由于FPGA的可重构特性,为系统的软件算法以及硬件结构的进一步优化升级打下了良好的基础,具有良好的应用前景。

评论