高速数据采集系统中的存储与传输控制逻辑设计

随着信息科学的飞速发展,数据采集和存储技术广泛应用于雷达、通信、遥测遥感等领域。在高速数据采集系统中,由ADC转换后的数据需要存储在存储器 中,再进行相应的处理,保证快速准确的数据传输处理是实现高速数据采集的一个关键。由于高速ADC的转换率很高,而大容量RAM相对ADC输出速度较慢, 保持高速数据存储过程的可靠性、实时性是一个比较棘手的问题。对于数据采集系统中的大容量高速度数据存储、传输,本文提出一种基于FPGA的多片RAM实 现高速数据的存储和传输的方案,并应用于1GS/s数据采集系统中,实现了以低成本RAM完成高速实时数据存储系统的设计。

本文引用地址:http://www.amcfsurvey.com/article/83041.htm方案选择

高速的数据采集速度是保证数据采集精度的标准,但往往在数据处理时并不需要以同样的速度来进行,否则对硬件的需求太高,成本也较高。这就需要有一个数据缓存单元,将数据有效地存储,再根据系统需求进行数据处理。

通常构成高速缓存的方案有三种。第一种是FIFO(先进先出)方式。FIFO存储器就像数据管道一样,数据从管道的一头流入,从另一头流 出,先进入的数据先流出。FIFO具有两套数据线而无地址线,可在其一端写操作而在另一端读操作,数据在其中顺序移动,因而能够达到很高的传输速度和效 率,且由于省去了地址线而有利于PCB板布线。缺点是只能顺序读写数据,不易灵活控制,而且大容量的高速FIFO非常昂贵。

第二种是双口RAM方式。双口RAM具有两套独立的数据、地址和控制总线,因而可从两个端口同时读写而互不干扰,并可将采样数据从一个端口 写入,而由控制器从另一个端口读出。双口RAM也能达到很高的传输速度,并且具有随机存取的优点,缺点是大容量的高速双口RAM的价格很昂贵。

第三种是高速SRAM切换方式。高速SRAM只有一套数据、地址和控制总线,可通过三态缓冲门分别接到A/D转换器和控制器上。当A/D采 样时,SRAM由三态门切换到A/D转换器一侧,以使采样数据写入其中。当A/D采样结束后,SRAM再由三态门切换到控制器一侧进行读写。这种方式的优 点是SRAM可随机存取,同时较大容量的高速SRAM有现成的产品可供选择。

从降低成本上考虑,采用第三种方式实现大容量数据存储功能。结合1GS/s数据采集系统的要求,存储深度为4MB。选择ISSI公司的静态RAM,由8片IS61LV25616构成4MB测试数据的存储,系统结构如图1所示。

图1 数据存储原理框图

数据存储设计

● 数据流控制

ADC为双通道500MS/s的转换率,8bit的垂直分辨率,转换数据的输出是每通道I、Q两个方向上差动输出,在差动时钟500MHz 的驱动下,可以实现1GS/s的实时采样率,由ADC输出的4路转换数据流输出分别为250MS/s。而IS61LV256系列RAM的速度级别为 10ns或12ns,这样数据必须经过FPGA进行缓存以后,才可以再次存入RAM。

IS61LV25616系列RAM芯片有16位数据线,18位地址宽度,同时还包括数据读RD、写WR及片选CS等控制信号。将8片RAM并行连接到FPGA上,组成数据采集的存储单元。

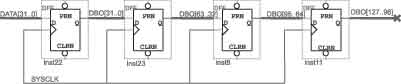

将从ADC输出AI[8...0]、AQ[8...0]、BI[8...0]、BQ[8...0],每路信号都为LVDS输出,共32位为 一组转换数据DATA[31...0],速率为250MS/s,要将这个速度在FPGA内部降至RAM可接受的范围。选用CycloneII系列 FPGA,其内部时钟可工作在402.5MHz,支持单端和高速差动标准I/O接口,对于250MS/s的数据流完全可以接收。利用FPGA内部的D触发 器作为缓冲,经过4级缓冲之后分别得到DBO[127...0],这样数据速度降为62.5MS/s。经过缓冲后的数据已经在选用的RAM接受速度级别 内,将得到128位的数据作为8片RAM的数据线,完成了数据流的控制。数据缓冲的原理如图2所示。

图2 数据缓冲设计

● 地址发生器设计

每次读写数据时,必须提供数据的存储位置,以读写信号作为时钟计数信号,顺序产生地址信号,其中NWE是RAM的写数据信号,NOE是读数 据信号,二者都是低电平有效,选择AB[17...0]作为RAM组的地址信号。CNTEN是地址计数器的使能信号,由读取/写入数据的深度决定,当未完 成读取/写入的数据时,CNTEN=0,此时允许读/写操作继续执行;当读/写操作完成时,相应的地址信号将CNTEN设置为1,则停止地址计数。地址发 生器的原理如图3所示。

图3 地址发生器设计

评论