基于ARM的2M测试系统

1引言

本文引用地址:http://www.amcfsurvey.com/article/82975.htm数字通讯飞速发展的今天, 2M口日益成为重要的设备投入业务测试点和运营维护测试点。数字通讯飞速发展的今天,建立综合业务数字网正成为电信经营者努力的方向。差错(误码、误块)性能作为数字网的重要传输性能指标,是网络营运者进行数字网建设、维护的重要依据;也是评估电信业务性能优劣的标准之一。 因此,国际电联(ITU-T)极为重视对差错的研究,近年来,针对数字网的设计、安装、维护的要求,推出了一系列有关误码性能的建议。目前我国工程技术人员所使用的测试仪多为国外进口产品,产品价格昂贵。而国产的测试仪功能相对简单。为此我们研究设计了一款基于 ARM的2M传输口测试系统。2Mb/s是我国数字时分复用基群2048kbit/s 的简称,是PCM传输与交换的基础。本文涉及的2M传输口测试系统为手持式PCM 2M综合测试仪器。

2系统硬件设计

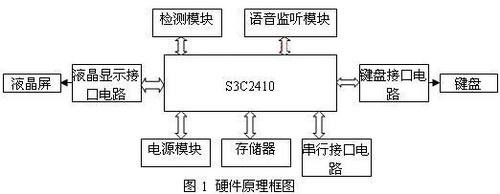

根据2M测试系统的性能要求,硬件层主要由系统核心部分、检测模块部分和语音监听部分组成。硬件原理框图如图1。

2.1 系统核心组成设计

在此系统中我们选用三星公司的S3C2410[1]微控制器芯片,内含一个由ARM公司设计的16/32位ARM920T RISC处理器核,ARM920T为低功耗、高性能的16/32核。S3C2410微控制器芯片在本系统中的主要作用是:(1)读写和控制各模块芯片;(2)读取键值;(3)控制液晶屏的显示;(4)在测量时进行数据的读取和处理;(5)对存储器进行读写;(6)通过串行口与微机进行通讯,将测试结果上传微机。存储器以HY29LV160 FLASH作为程序存储器,以HY57V641620 SDRAM作内存,构成嵌入式系统核心。S3C2410芯片内含一个IIC总线控制器,可方便的与各种带有IIC接口的器件相连。在该系统中,外扩一片AT24C01作为IIC存储器。可存放在系统掉电时需要保存的数据。

2.2 检测模块部分的设计

检测模块部分由芯片DS21354[2]和芯片DS21372组成,这两块芯片协同工作共同完成检测功能。DS21354芯片主要完成发送和接收2048kbit/s 的PCM 信号,并从中检测误码和告警状态。DS21372是一种软件可编程的测试图样产生、接收、分析器,能适用于对差错性能要求最严格的数字传输设备的能力。具有两种测试图样的生成方式(伪随机序列和重复序列)。符合CCITT/ITU O.151,O.152,O.153和 O.161标准。DS2172 可以工作在直流到20MHz,这样宽的频率工作范围使它可以灵活地使用在现有的设备和处于测试阶段的新设备中,如:传输设备,交换设备,复用器,DAC,路由器,桥设备等。

DS21372[3]中包含有4个功能块:图样产生,图样检测,差错计数和控制接口,具有完全独立的传输和接收部分,8bit的并行处理器接口,可以编程产生最大长度为(232-1)bits的伪随机序列图样,可编程的多项式长度和反馈量可以用于任意伪随机序列图样的生成,包括: 26-1、29-1、211-1、215-1、220-1、223-1和232-1。或者用户编程的自定义长度从1到32bits的重复序列图样。拥有32bit差错计数器和比特计数器。软件编程的比特差错插入,最大比特差错率图样的检测可达10-2。DS21372能向线路插入单个bit或从10-1bit到10-7bit误码率的误码,以检验设备的操作状态和连通性。用于分析、评测、解决数字通信系统中出现的问题。

2.3 语音监听模块部分的设计

语音监听部分采用时隙交换电路和语音检测模块组成,语音检测模块采用ZARLINK的3.3V多功能CODEC MT91L60[4]。这款芯片能实现声音信号的A/D、D/A转换,并为标准的电话机手柄等接收发送装置提供模拟接口。当E1接口电路与2M实际线路连通后,2M 链路上的话音时隙要通过时隙交换电路与MT91L60电路相连,构成了话音时隙收发的通道。在这个过程中要初始化时隙交换电路,将2M链路上的需要监测的话音时隙交换至MT91L60。打开MT91L60接收通路至电话机手柄输出,设置ITU-T A-law话音编码方式,设置接收增益+6dB,设置非消侧音非环回模式等。这些设置是通过设置MT91L60内部寄存器完成的,完成这一系列设置后,语音测试就可以开始了,语音可以通过电话机手柄听到,其他测试内容可以从MT91L60内部寄存器读到结果。

评论