RocketIO的高速串行通道设计与验证

引 言

目前,多数计算机、嵌入式处理设备和通信设备都采用并行总线,但随着芯片性能不断提升和系统越来越复杂,数据传输带宽已成为提高系统性能的瓶颈。虽然增大并行总线宽度可以提高芯片与芯片之间、背板与背板之间的数据吞吐量,但是数据线的增多和传输速率的加快会使PCB布线的难度提高,并且增加了信号延时和时钟相位偏移。高速串行互连技术成为提高数据传输带宽的有效解决途径。

新的串行总线技术不断涌现,如新推出的串行总线标准有PCI-express、RapidI()、10Gigabit Ethernet Attachment Unit Interface(XAUI)、HyperTransport、Infini-Band、SATA等。新标准的快速发展及网络与通信领域不断增强的数字统一趋势,对系统设计人员桥接这些标准和适应不断演化的标准提出了新的挑战,需要具有新一代系统集成和灵活性的可编程解决方案。Xilinx公司的Vir-tex-4 FX系列FPGA芯片内置了RocketIO收发器,能够提供622 Mb/s~6.5 Gb/s的数据传输速率,并且支持多种高速串行通信协议,可以帮助设计人员方便、灵活、可靠地实现高速通信。

1 设计要素

1.1 时 钟

在Virtex-4 FX系列FPGA中每个RocketIO Multi-Gigabit Transceiver(MGT)有多个时钟输入。其中,参考时钟有3种,根据不同的传输速率选择不同的参考时钟。GREFCLK适用于单个MGT组且数据传输率低于1 Gb/s的情况。REFCLK1和REFCLK2一般用于数据传输率高于1 Gb/s、低于6.5 Gb/s的情况。

时钟精度和时钟抖动是评价时钟质量的两个重要指标。MGT模块要求高精度的参考时钟,MGT要求的时钟精度为±350×10-6,MGT可容忍的输入参考时钟抖动公差最大为40 ps,所以从DCM中出来的时钟(大于±100ps)不能够作为MGT的参考时钟输入。MGT的时钟一般采用以下方案解决:从片外输入的差分时钟必须经过RocketIO模块指定的差分时钟引脚接入,然后经过Rock-etIO模块中的时钟管理模块GTllCLK_MGT转化成单端时钟,送到REFCLK1或REFCLK2作为MGT的参考时钟。

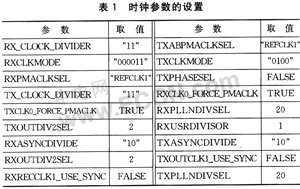

MGT模块的输出时钟TXOUTCLK1、TXOUT-CLK2、RXRECCLK1、RXRECCLK2可以作为4个用户使用的时钟TXUSRCLK、TXUSRCLK2、RXUSRCLK、RX-USRCLK2的时钟源;也可以作为DCM模块的输入,从而生成用户所需的特定频率的时钟,提供给系统其他模块使用。参考时钟的频率由串行传输速率和时钟参数设置来决定。表1是该实验中关于时钟参数的设置。

1.2 复 位

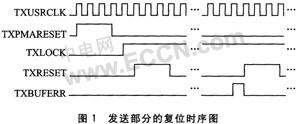

MGT模块中的复位分为发送部分的复位和接收部分的复位。发送部分的复位主要包括TXPMARESET和TXPCSRESET;接收部分的复位主要包括RXPMARE-SET和RXPCSRESET。TXPMARESET复位用于复位PMA和重新初始化PMA功能。其引脚电平为高时,复位PLL控制逻辑和内部的PMA分频器,同时也使发送器PLL LOCK信号为低并且迫使TX PLL进行校验。TXP-MARESET引脚电平为高至少要持续3个USRCLK时钟周期。

当TXPCSRESET引脚电平为高时,TX PCS模块被复位。TX PCS模块包括:TX Fabric接口,8B/10B编码器,10GBASE-R编码器,TX缓冲器,64B/66B扰码器和10GBASE-R自适应同步器。TXPCSRESET复位与TXPMARESET复位是相互独立,互不影响的。

TXPCSRESET复位的要求如下:

①在TXPCSRESET复位时,TXUSRCLK和PCS的TXCLK时钟必须已经保持稳定,以便初始化发送缓冲器。

②TXPCSRESET引脚电平为高,至少要持续3个TXUSRCLK或TXUSRCLK2时钟周期。

③在TXPCSRESET复位结束后,TX PCS模块至少需要5个时钟周期(以TXUSRCLK或TXUSRCLK2中最长的时钟周期为准)来完成各个子模块的复位。

图1是发送部分的复位时序图。接收部分的复位时序图和复位要求与接收部分类似,请参见Xilinx公司技术文档ug076.pdf。

2 MGT的模块及原理介绍

发送的并行数据经过8B/10B编码后,写入发送端FIFO,然后转换成串行差分数据发送出去。接收端接收到的串行差分信号首先经过接收端缓冲,然后经过串并转化器转换成并行数据,再经过8B/10B解码,写入弹性缓冲,最后并行输出。

2.1 8B/10B编解码器

8B/10B编码机制是由IBM公司开发的,已经被广泛采用。它是一种数值查找类型的编码机制,可将8位的字符转化为10位字符。转化后的字符可以保证有足够的跳变用于时钟恢复。8B/10B编码具有“0”和“1”出现的概率相等,直流基线漂移小,低频分量小,功率谱带宽较窄,抖动小,以及能够检测输入数据中的错误等许多优点。

8B/10B编码可以分为256个数据字符和12个控制字符。数据字符,标为D,用于传输数据;控制字符,标为K,用于传输控制序列。12个控制字符用于对齐、控制,以及将带宽划分为子通道。

2.2 comma字符检测和对齐

Virtex-4 RrocketIO有可编程的逗号检测,以便于实现10位字符的各种通信协议和检测,通过对MCOMMA_10B_VALUE、DEC_MCOMMA_DETECT、PCOMMA_10B_VALUE、DEC_PCOMMA_DETECT和COMMA_10B_MASK这些参数的设置,可以实现任意的8位或10位符号检测。

接收器在输入数据流中扫描搜寻comma字符。如果找到,解串器就调整序列边界以匹配检测到的comma字符序列,且扫描是连续进行的。一旦对齐确定,所有后续comma字符的对齐均已确定。在任意的序列组合里,comma字符序列必须是唯一的。常用的K字符是12个K字符中的一个或多个。由于K28.1、K28.5、K28.7这些字符的头7位都是1100000,这种比特序列模式只可以在这些控制字符中出现,因此,这些控制字符是非常理想的对齐序列。

2.3 时钟修正

在时钟/数据恢复电路的作用下,从接收的串行数据流中解出时钟的频率和相位,一般将它的20分频时钟作为恢复时钟。在恢复时钟作用下从串行数据经过解串器产生并行数据作为8B/10B译码的输入,译码后的数据进入16×52位的接收缓冲器。输入缓冲器的输人数据速率是由PCS RXCLK的频率决定的,而从缓冲器读取端输出的数据速率是由RXUSRCLK的频率决定的。由于两个时钟会有差异,所以需要进行时钟修正。

时钟修正的基本原理是:在发送端,当数据发送了一定的字节或数个数据包后,通过插入和发送一些特定的字节修正字符;在接收端,当接收到这些字符后会自动地丢弃或者重复来补偿时钟的差异。时钟修正的核心工作是在比特流中搜寻特定的字符序列。

3 MGT的测试与验证

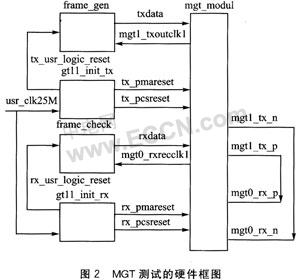

本实验是在XilinX公司的ML405评估板上进行的,使用2个MGT。其中,MGT1用来发送数据(通过mgt1_tx_n和mgt1_tx_p这对差分线),MGT0用于接收数据(通过mgt0_tx_n和mgt0_tx_p这对差分线)。使用串行ATA电缆(长约100 cm)将它们连接起来形成一个大环路,进行数据读回测试。MGT验证实验的硬件框图如图2所示。

其中,gtll_init_tx模块产生tx—pmareset、tx_pcsreset复位信号以及frame—gen模块的复位信号;frame—gen模块产生带有comma字符的数据流,每次发送的数据位宽为32位;gtll_init_rx模块产生rx_pmareset、rx_pcsreset复位信号以及frame_check模块的复位信号;frame_check模块用来将发送的数据与实际接收到的来自于MGT0的并行输出端口的数据进行比较,如果检测到不一致,则frame_check模块的ERR_COUNT计数器就加1,通过读取该计数器的值和记录MGT工作的时间就可以计算出该系统中MGT的错误率。

假设MGT的错误率为δ,MGT的数据传输率为μ,MGT传输数据的有效时间为τ,ERR_COUNT计数器的计数值为E,则有:

![]()

实验中测得,E=319,τ=3 600s,μ=3 Gb/s。将上述数值代入式(1),求得δ=2.957×10-11。通过取不同的时间τ,每个τ对应做多次实验,可以得到δ的范围为[2.752×10-11,3.168×10-11]。通过该实验可以发现具MGT的可靠性比较高,可以满足我们的工程需求,具有很高的实际使用价值。

结 语

目前,系统对数据传输率的要求越来越高,高速串行互连技术由于将时钟与数据合并进行传输,从而解决了高速并行数据传输过程中时钟和数据的抖动问题,提高了数据传输速率,降低了设计复杂性和成本,减少了引脚数量和PC板面积。Xilinx公司的Virtex-4 FX系列FPGA器件中所提供的用于实现高速串行互连的RocketIO IP核,具有使用方便、配置灵活、集成度高等优点,将它用于解决高速串行数据传输问题,既简化了设计,又提高了系统的集成度和可靠性,有很好的应用前景。

linux操作系统文章专题:linux操作系统详解(linux不再难懂) 分频器相关文章:分频器原理

评论