实现可靠的高性能数字电源

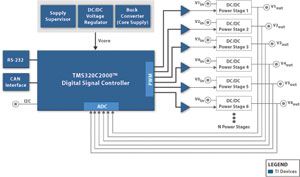

在研究数字电源转换设计时,设计人员还必须考虑为控制电路和DSC本身供电的辅助电源。图2中的DSC支持单输入电压并且具备必需的电源管理功能,从而简化了辅助电源电路,提高了可靠性。

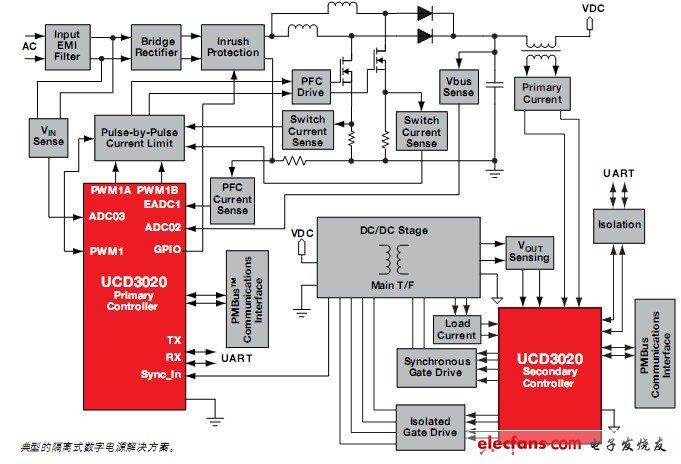

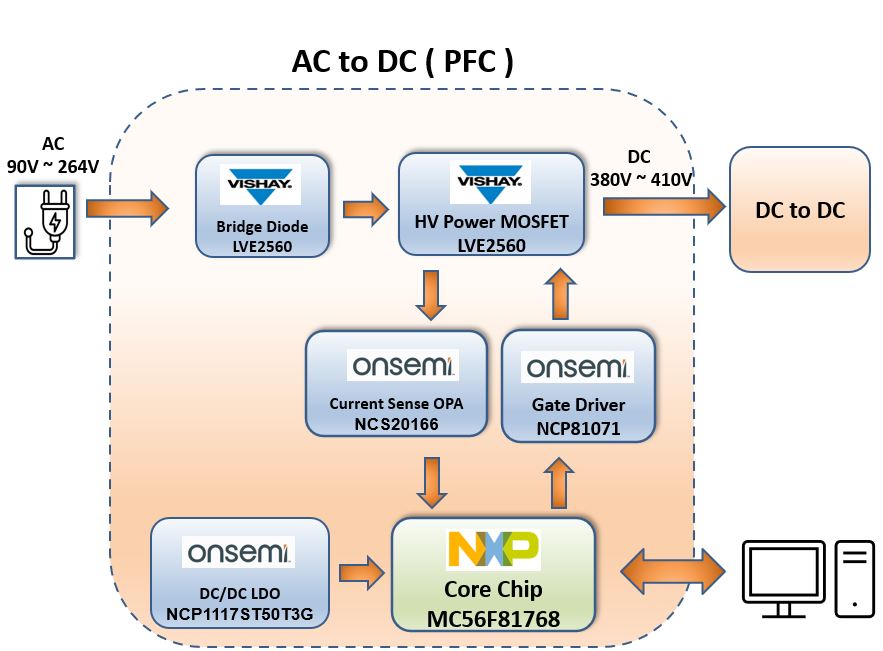

本文引用地址:http://www.amcfsurvey.com/article/82434.htm在诸如AC至DC转换器的某些应用中,器件可执行AC至DC转换控制以及诸如功率因数校正(PFC)等功能。支持增加诸如PFC等功能的数字PWM功能模块是PWM互补输出对的独立时基。通过使用“备用”PWM信号和运行在DSC上的软件即可实现上述功能,无需外部PFC芯片,从而进一步增加了电源的可靠性。

实现数字回路

典型拓扑结构的数字控制回路示例将说明DSC或其他拓扑结构的选择会对设计产生怎样的影响。图3显示了一个同步降压转换器。这种结构之所以称为同步降压转换器是因为晶体管Q2的开关与主开关Q1同步。同步降压转换器的设计理念是将MOSFET用作与标准整流器相比具有极低正向压降的整流器。当二极管的电压下降时,降压转换器的整体效率将会提高。同步整流器(MOSFET Q2)还需要一个与主PWM信号互补的PWM信号。Q2会在Q1关断时导通,反之亦然。这种PWM形式被称为“互补的PWM”模式。

图3 同步降压转换器

图4 SMPS控制系统示例

图4描绘了一个SMPS控制回路示例。最需要注意的是图中的每个模块都有相关的延时。采样/保持电路通常每2到10微秒采样一次,且ADC需要约500纳秒将模拟反馈信号转换为数字值。

比例-积分-微分(PID)控制器是运行在DSC上的一个程序,其计算延时约为1至2微秒。该控制器的输出被转换为一个PWM信号,由该信号驱动开关电路。若在设定新的占空比后,PWM发生器不能立即更新其输出,就会引入相当大的延时。此外,根据所用的器件和电路的设计,晶体管驱动器和相关晶体管引入的延时在50纳秒到1微秒。输出滤波器通常由电感和电容电路构成,同样会导致较大的延时。

与模拟反馈信号转换、处理器的数字计算以及数字PWM信号输出给功率晶体管的延时相关的所有延时都被加到采样速率延时。主控制回路的有效采样频率是控制器延时和采样延时的倒数。在本示例中,控制延时是4.1微秒,因此采样速率大约为244 kHz。

控制器带宽是控制器的有效采样速率与过采样比之商。一般来说,回路稳定工作要求6至10倍的过采样。在本示例中,需要6倍的过采样比来实现所需的回路性能。估计控制器带宽为40 kHz。在控制算法中加入前馈控制项可提升控制器的性能,使其性能超越带宽为40 kHz的传统PID控制器。

了解了这么一个示例以后,让我们看看采用这样的基本回路如何达到电源应用的某些架构需求。要防止PWM信号的波动对控制器产生影响,要求PWM重载频率应至少比DSC带宽高4或5倍。本示例中两者的比为10:1,这样就要求将PWM频率设置为400 kHz。一旦设置了PWM重载频率,就可据此确定PWM分辨率。

许多供应商和客户均对“PWM分辨率”这一术语感到困惑。PWM分辨率并非指特定计数器的宽度,而是指在一个PWM周期内的计数值(可能的最小PWM时间片段)。在电源行业中,PWM分辨率指定为一个PWM周期中可达到的最小时间增量,通常单位为纳秒。如果DSC的数字PWM模块不具有足够的分辨率,控制系统(硬件或软件)将会使用dither(扰动)处理方法对输出进行调整以实现期望的平均输出。在电源应用中,PWM扰动会导致电流纹波问题并使控制进入不理想的“极限循环”工作模式。

PWM分辨率 = PWM计数器频率 / PWM频率

已经为设计选择好了PWM频率,还必须确定所需的PWM分辨率。本示例要求约11位的分辨率,因此PWM时钟必须工作在约1 GHz的频率下。

控制算法由SMPS软件实现,其中的核心就是PID循环。PID软件通常比较小,只有1到2页的代码,但其执行速率非常高,通常每秒可以进行几十万次迭代!

这样高的迭代速率要求PID软件程序必须足够高效以使性能最佳。汇编器提供了确保“代码紧凑”的好方法。

PID软件的执行时间确定了两个系统性能指标:

1. PID迭代速率,由它确定控制回路更新之间的时间。

2. PID执行时间,是反馈采样和PWM更新之间的关键路径。

ADC以固定的时间间隔中断,供DSC执行PID控制循环。任何可在“闲置循环”内执行的系统函数均应在PID控制软件循环外执行。诸如升压/降压、错误检测和前馈计算等函数,以及通信支持程序均可在闲置循环内执行。任何其他由中断驱动的进程(比如通信)的优先级必须低于PID循环。

设计数字电源转换软件时可遵循如下指导方针:

.推荐采用汇编语言编写执行速率极快的内部PID循环

.PID执行时间会影响稳定性

.PID迭代速率会影响稳定性

.PID处理器的负载不超过其额定值的66%

.在闲置循环中执行“辅助函数”。

数字电源转换需要某些独特的ADC采样功能,来实现不需要过多处理功能的实际应用。系统中实现了一个控制回路,DSC在该回路中通过PWM状态驱动被采样的信号。系统了解何时采样感兴趣的信号以提供最多的信息。图5说明了在PWM驱动信号的精确位置触发ADC转换的重要性。

图5 异步ADC采样示例

要使电源转换器应用的设计成本最低,最好是能够对系统中接近地电位的位置测量电压和/或电流。这样省去了处理直接监视通过电感“L”的电流所需的大共模电压的电路,从而降低了成本和复杂性。

在本例中,当晶体管导通时电感电流流经晶体管。应当测量晶体管关断时的瞬态峰值电流。如果用户无法在正确的时候捕捉电流采样(比如采样延时),晶体管将处于“关断”状态。若在晶体管关断时采样,因为没有电流流经检测电阻“R”,因而测量不到电流。采样延时比测得不良数据更糟糕——因为根本就没有数据!

评论