基于Nios II的I2C总线接口的实现

0引言

本文引用地址:http://www.amcfsurvey.com/article/82352.htmI2C(Inter-Integrated Circuit)总线是一种由Phil-ips公司开发的两线式串行总线,用于连接微控制器及其外围设备。由于I2C总线仅用两根信号线,并支持多主控工作方式,所以I2C总线在电子产品设备中应用非常普遍。文献[1]使用NiosⅡ的PIO接口模拟I2C时序完成对接口芯片的读写,而目前基于NiosⅡ的IP核越发丰富。基于此,本文使用免费的IP核--I2C-Master Core,实现了对I2C接口芯片的读写操作,扩充了一种新的设计方法。本文首先介绍了I2C总线结构和工作原理,然后详细说明了基于NiosⅡ的I2C-Master Core的使用方法,最后给出了C语言的编程代码。

1 I2C总线基本原理

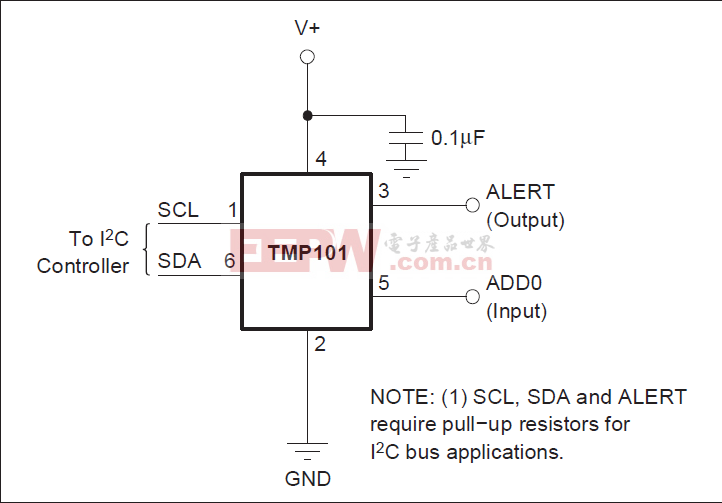

I2C总线是由数据线SDA和时钟SCL构成的串行总线,可发送和接收数据。在CPU与被控IC之间、进行双向传送,最高传送速度100 kbit/s。

I2C总线在传送数据的过程中共有4种基本类型信号,分别是:开始信号、数据传输信号、应答信号和结束信号。

a)开始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。所有的命令都必须在开始条件以后进行。

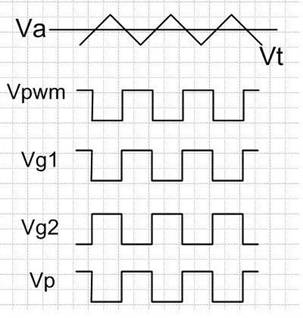

b)结束信号:SCL为低电平时,SDA由低电平向高电平跳变,结束传送数据。所有的操作都必须在停止条件以前结束。总线开始和停止数据传送的时序如图1所示。

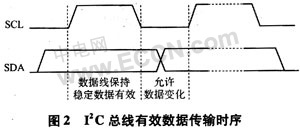

c)数据传输信号:在开始条件以后,时钟信号SCL的高电平周期期问,当数据线稳定时,数据线SDA的状态表示数据有效,即数据可以被读走,开始进行读操作。在时钟信号SCL的低电平周期期间,数据线上数据才允许改变。每位数据需要一个时钟脉冲。I2C总线的数据位传送时序如图2所示。

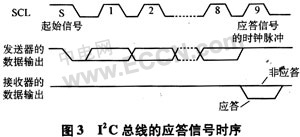

d)应答信号:接收数据的从器件收到8 bit数据后,向发送数据的主控器件发出特定的低电平脉冲,表示已收到数据。这要求主器件必须产生一个与确认位相应的额外时钟脉冲(第9个脉冲)。若主控器件确认失败,主控器件必须发送一个数据结束信号给从器件。这时从器件必须使SDA线保持高电平,使主控器件能产生停止条件。总线的应答信号时序见图3。

2 I2C接口芯片AT24C01/02工作原理

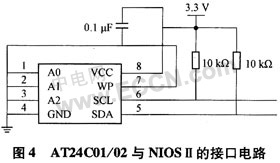

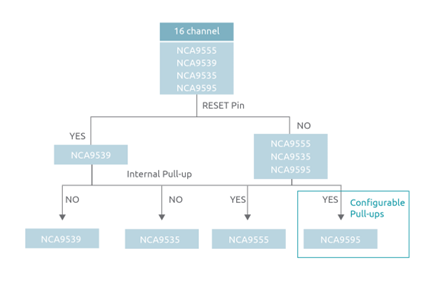

AT24CXX系列芯片是采用I2C总线标准的常用的串行EEROM芯片。本文以AT24C02为例介绍。AT24C02具有256×8(2 k)bit的存储容量,即总共32页,每页有8字节的容量。每次写入数据是从主器件发送来的片内选择地址开始写人,如果写到页末尾,主器件还在继续发送的话,不会自动转到下一页,而是从该页的头地址开始继续写入,覆盖该页的原有数据,而造成数据丢失。AT24C02工作于从器件方式,它的地址由外围的3个引脚A2、A1、A0决定,如图4所示。在I2C总线上总共可以连接8个AT24C02接口芯片,每个器件硬件地址与控制寄存器的地址内容保持一致,就能够自由地与主控器件进行数据传输。

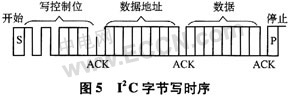

1)器件字节写操作

在字节写模式下,发送器件写控制字,控制字包括4位固定器件码,3位片选码,以及一位低电平的写控制位。主器件在收到从器件产生应答信号后,主器件发送一个8位字节地址写入AT24C02。主器件在收到从器件的另一个应答信号后,再发送数据到被寻址的存储单元。AT24C02再次应答,并在主器件产生停止信号后开始内部数据的擦写,在内部擦写过程中,AT24C02不再应答主器件的任何请求。时序见图5。

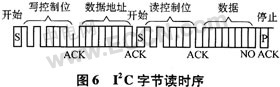

2)器件随机地址读操作

对AT24C02读操作的初始化方式和写操作时一样,仅把R/W位置为1。图6所示为AT24C02随机地址读时序图。随机读操作允许主器件对寄存器的任意字节进行读操作,主器件首先通过发送起始信号、从器件地址和它想读取的字节数据的地址执行一个伪写操作。在AT24C02应答之后,主器件重新发送起始信号和从器件地址,此时R/W位置1,AT24C02响应并发送应答信号,然后输出所要求的一个8位字节数据,主器件不发送应答信号但产生一个停止信号。

3 I2C-Master Core工作原理

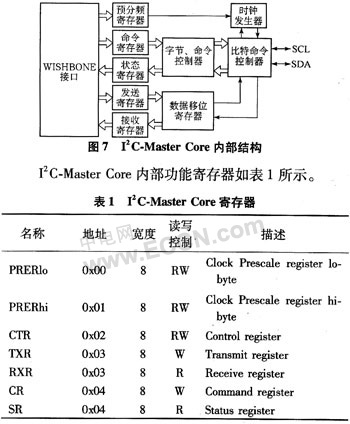

基于NiosⅡ的IP核应用非常简便,因此越发受到青睐。Altera公司已经提供了一些通用的IP核可供使用,但没有提供I2C核。文献[3]提供了免费的I2C-Master Core,经笔者的应用与长时间测试,证明该Mas-ter Core使用方便可靠,工作稳定。该Master Core的内部结构如图7所示,主要由时钟发生器、字节命令控制器、比特命令发生器和数据移位寄存器4个模块组成。其他模块是一些相关接口和临时数据存储器。

时钟发生器主要是产生SCL信号,该时钟的频率可由预分频寄存器设置,控制子计算公式如下:

![]()

例如:SCL频率为100kHz,NiosⅡ工作频率为50 MHz,则预分频=99,PRERlo=99,PRERhi=0。

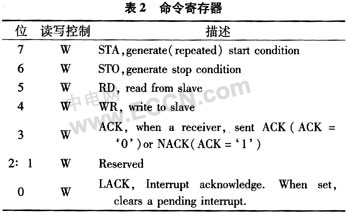

字节命令控制器在字节级连接命令寄存器、状态寄存器和比特命令控制器。通过将表2所示命令寄存器相应的比特位置1,可以产生I2C接口的开始、结束、确认等信号,以及读写控制。这些有效控制通过字节命令控制器转送到比特命令控制器,使其发生作用,在信号产生后,这些比特位自动清0。

NiosⅡ向发送寄存器写数据实现数据输出,读接收寄存器获取从器件输出的数据。数据的读写是否完成可通过中断或查询方式得知。如采用中断方式,状态寄存器中的IF状态位置1;如采用查询方式,数据处理过程中,状态位TIP置1,处理完毕后置1。

4应用实例

笔者在NiosⅡIDE7.1环境下编写了使用该Mas-ter Core的C语言代码,现把部分主程序代码列出。

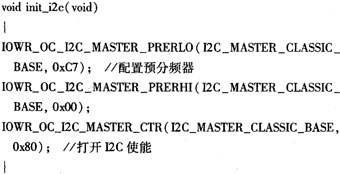

1)IP-Master Core初始化

完成对预分频器的设置,确定SCL时钟频率;控制寄存器中I2C-Master Core使能位置1,使其工作。

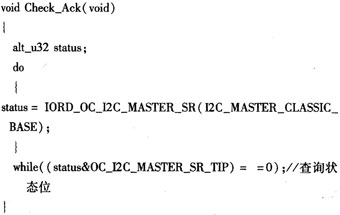

2)查询确认信号

数据收发是否完成,通过查询TIP状态位来确定。

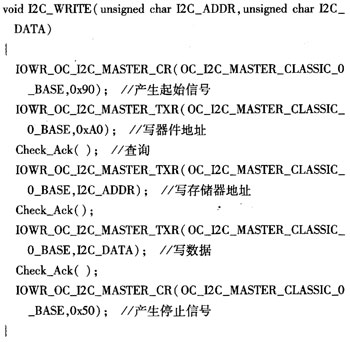

3)写字节操作

单字节写入按图5操作流程:

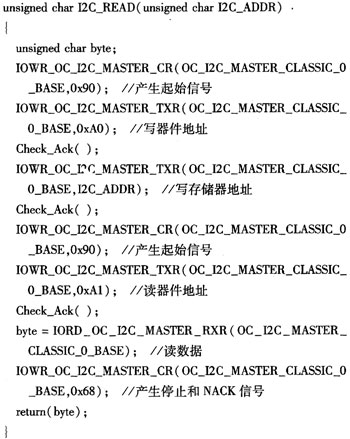

4)随即地址读操作

随即地址读字节按图6流程操作:

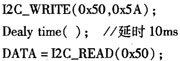

以上是使用I2C-Master Core的关键代码,若向地址0xS0写入0x5A,再将其读出,可按下面写法:

若操作正确,DATA的值应该位为0x5A。

5结束语

本文探讨了使用免费I2C-Master Core的方法,方便地实现了基于Nios Ⅱ的I2C接口芯片的开发,为I2C的电子工程设计使用提供了一种简单快捷的方法。

分频器相关文章:分频器原理

评论