降低功耗:小心“过度设计”

当前,降低功耗不仅成为节电的必由之路,并且被赋予了环保的神圣使命。因此所有的设计者都十分关心功耗问题。不过,在设计时还要谨防过度设计(overdesign)现象,使各个部分协调一致,达到整个功耗的降低。

本文引用地址:http://www.amcfsurvey.com/article/82226.htm应用是个很复杂的问题,其中有许多要素。你需要针对问题提供整体化的解决方案。在深刻理解最终应用的情况下,你会发现是否出现了过度设计;有时候,出于市场等方面的考虑,会出现过度设计的做法,这最终会导致功耗过高。

系统设计与SoC设计的相对比例问题,软、硬件比例问题,IC的驱动电压是否越低就越好?制造技术节点是否越小越好?都是值得考虑的因素。

在近日旧金山举行的Electronic Summit2008上,ON Semi(原AMI Semiconductor,2007年12月被收购)高级Hearing/Audio Solutions总监Michel De Mey以DSP设计为例,说明了功耗更加取决于整体架构的合理。例如音频用低功耗DSP,如耳机,蓝牙耳机等等靠极小的电池供电的微型应用,在这些应用中,电池的供电时间很关键。一个应用就是滤波,你可以在时域或者频域进行滤波。例如,如果你能在频域实现滤波,就可以将功耗降低10倍。这可不像从哪里挤出20%来,而是从体系架构上进行创新,从而达到如此之高的比例。如果你将它们与,例如双Quad(dual-Quad)架构,结合起来,实现负载的均衡化。从硬件实现出发,如果实现了两个Quad的负载平衡,则对这两个石英的频率的要求就较为宽松,你就可以在其它性能实现方面花费更多的时间,如时序的闭合,尝试不同的频率、大大降低电源电压等等。采用这种技术(恰当的负载平衡、SoC技术)后,我们还能再挤出2~3倍的改进余地。

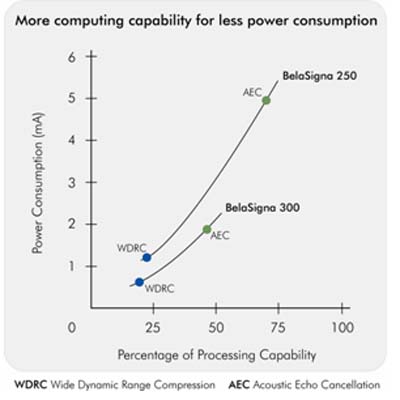

例如,On Semi的第二代DSP产品与前代产品比较,即Bolosigno 300和Bolosigno250比较。两种产品的硬件都执行同样的功能,区别在于,它们分属不同的技术节点(制程),采用了不同的DSP架构。On Semi更换了内存技术,降低了内存的电压,而且让存储变得更为分布化一些。采用了更新的模拟和数字IP、新的设计方法学、以及新的EDA工具,其功能也取决于你的算法。如果你采用了运算密集的算法,使得内核达到了50%~60%的负载,可以让性能提高3倍;如果你对内核进行20%的加载,则性能也可以提高2倍。

图:Bolosigno 300和Bolosigno250的功耗比较

那么低功耗是否意味着低电压?Michel认为功耗不仅取决于你是否用1.0V还是1.2V,更取决于算法的速度。

评论