CMOS场效应晶体管的发展趋势

前言

本文引用地址:http://www.amcfsurvey.com/article/81597.htm自从1947年第一支晶体管的发明,半导体集成电路在二十世纪的后三十年有了一个极大的发展。这个发展极大的推动了世界性的产业革命和人类社会的进步。 今天在我们每个人的日常生活中, 英特网,手机的普及和计算机在各个领域的大量应用,已经使我们进入了信息时代。在这中间起决定性作用的是在硅晶片上工作的CMOS场效应晶体管的发明,它的制造工艺的不断发展和以它为基础的超大规模集成电路的设计手段的不断改进。

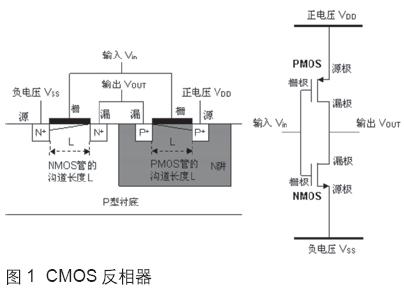

图1是一个最基本的CMOS逻辑门—反向器的物理结构和电路图。当输入为逻辑0时它的输出为逻辑1,当输入为逻辑1时它的输出为逻辑0。它是构成超大规模集成电路的一个最基本的元件之一。在这个电路里有两个我们必须要考虑的最重要的参数。

一个是它的功耗PD,另一个是场效应管的沟道长度L。 对于第一个参数我们必须要让它的值最小,这样我们才可以在一个很小的硅晶片上集成上几百万个晶体管而不让它发热。CMOS数字集成电路相对于其它工艺的集成电路是它的功耗非常低。例如上面的反相器它的静态功耗几乎为零而它的动态功耗在纳瓦(nW)甚至在皮瓦(pW)级。因此现代集成电路几乎全部是用CMOS工艺。 关于第二个参数,是场效应管的沟道长度L。 我们也需要让它的值尽可能的小。这样器件的工作速度或频率就很高,因为沟道长度变小,管子的体积也随之减小,整个电路的集成度就高。根据CMOS 管的按比例缩小原理 [1],在一阶近似的情况下当管子的沟道长度和宽度同时变小a倍,在器件内建电场不变得情况下,它的工作电压将减小a倍,功耗将减小a2倍,而集成度将增加a2倍。同时管子的工作速度也增加a倍。由于这些原因,在全世界范围内,从CMOS场效应管工艺发明之日起,各大半导体制造公司都把减小场效应管的沟道长度作为研究与开发的最主要的重点。1965年美国的英特尔公司(Intel)的创始人G. MOORE总结了集成度随年份增长的数据,得出平均每一年在每一芯片上集成的平均晶体管数目将增加一倍的结论,称为 摩尔定律[2]。由于考虑到管子的数目增加,系统的功能也越来越复杂,G. MOORE本人在1975年修改了这条定律,把它从每一年改为每两年。但从半导体产业的发展情况看,实际结果是每十八个月。图2 是由英特尔公司提供的资料[3]。我们可以看到正是由于管子沟道长度的减小,集成度的提高,才使得半导体存储器和微处理机发展到今天这个水平。

但是,任何事物的发展都有两面性。由于CMOS场效应管沟道长度的减小,当它的值小到一定的时候,将被一些器件的物理参数和制造工艺的极限所限制。在这篇文章中,我们将讨论这些物理参数和制造工艺的极限并给出CMOS集成电路在21世纪前二十年的发展趋势。

CMOS场效应管的物理参数极限

·最小允许的场效应沟通道长度

我们知道MOS场效应管的一个最基本的功能是一个可控开关。在图3 中我们可以看到:当NMOS管的栅源电压VGS大于管子的阈值电压Vth时,MOS管导通就像一根导线一样。而当栅源电压VGS小于管子的阈值电压Vth时,MOS将进入截止区域,漏源电流IDS为零就像一个开路一样。

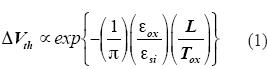

最小沟道长度对于一个CMOS场效应管来说是最关键的限制[4]。根据场效应管的微电子学原理,当沟道长度减小时,横跨场效应管漏极和源极区域的电场, 有时我们也称单向横场,将增加。作为一个结果,场效应管栅极控制管子沟道导通的能力将下降。这就是我们所说的场效应管的短栅效应[5]。而且这个效应随着漏极到源极电压的增加也变得越来越严重,直接导致场效应管的阈值电压Vth 的减小,亚阈值泄漏电流的增加。在这种情况下,场效应管将不能以我们所期望的理想的可控开关的形式来工作。根据MOS管的微电子学原理, 在一阶近似的情况下,MOS 管的阈值电压的变化DVth与管子的沟道长度L的自然指数成正比关系。 我们有[4]:

其中eox和esi分别是栅极氧化层和管子硅沟道的介电常数,Tox是栅极氧化层的厚度。从这个关系中我们看到,当管子的沟道长度L减小到与管子的栅极氧化层的厚度Tox在同一个数量级,管子的阈值电压将急剧的减小。 这就构成了最小允许的场效应管沟道长度。

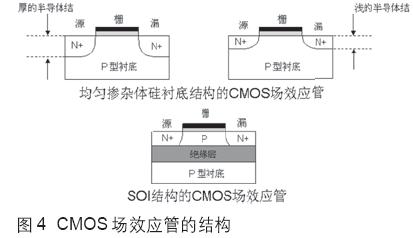

为了减小MOS 管的短栅效应,主要的科研工作是改进栅极对整个管子沟道的控制能力[4]。从这方面入手,在近二十年来,人们从薄的源极漏极扩散结到不同型式的沟道掺杂注入结构,从经典的体硅衬底到SOI(Silicon On Insulator), 大量的MOS场效应管结构已经被研究。图4给出了一些最重要的研究结果。今天人们从模拟的结果预测10至15纳米的沟道长度将是MOS管按比例缩小的物理极限[6]。更进一步,当管子的沟道长度小于这个尺寸,量子隧道效应将显著增加以导致MOS管的栅极将完全损失掉对沟道的控制能力,这样MOS管将不能完全截止导致它将不能完成最基本的开关功能。

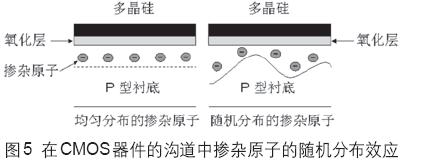

·沟通道掺杂源自排列的随机效应

根据MOS管的微电子学原理,在用离子注入时,掺杂原子在器件沟道位置的随机变化将影响MOS管电参数的变化。当MOS管的尺寸减小时,掺杂原子在器件中的平均数量将减小。作为一个结果,掺杂原子数目和它们在器件沟道中的所在位置的随机变化将增加[7]。图5 将说明这种情况。在标准的制造工艺中,掺杂原子通过随机散射过程在沟道中找到它们的所在位置。因此,掺杂原子在沟道中的数目和排列的随机效应是器件的固有效应,人们不能在标准的制造工艺中把它们取消掉。这个效应将导致器件和整个电路的性能, 例如电流的驱动能力和传输滞后的随机变化。其中掺杂原子在沟道中的数目和排列的随机效应也将引起MOS管阈值电压的随机变化。这些将直接导致由于沟道长度减小而使器件的性能变坏。

·耗尽层的厚度和半导体界的厚度

一般来说,为了减小MOS管的短沟 道效应, 器件的耗尽层的厚度和源极与漏极的半导体结的厚度要尽可能的薄。而器件的耗尽层的厚度和源极与漏极半导体结的厚度的形成是通过离子注入的方式控制要被注入的掺杂原子到被选中的区域和限制它们的热运动。当器件的尺寸减小时,理论计算要求现代MOS 管有一个较为陡峭的掺杂剖面[8]。在MOS管的制造过程中,这个陡峭的掺杂剖面要求对于控制耗尽层厚度和源极与漏极半导体结厚度的形成是一个极大的挑战。在这方面,SOI MOS场效应管结构是一个最好的选择。但是这种结构也有它的局限性,例如:高电场下的导电子的迁移率的减小和量子化阈值电压的变化[8]。

·最小栅极氧化层厚度

为了保证MOS管的短沟道效应在可控制的范围内和保持一个好亚阈值截止特性,正像关系式(1)所指出的那样,栅极氧化层厚度Tox需要减小到与场效应管的沟道长度L来比差很多倍[9]。例如:对于一个100纳米沟道长度的MOS管,在1.5 伏的工作电压下,它的栅极氧化层厚度应该是在3纳米的范围。这个3纳米的厚度大约相当于十个硅原子紧密排列的厚度[7]。对于这样一个氧化层厚度,量子力学的遂道效应将发生。这直接导致栅极的泄漏电流随氧化层厚度的减小而成指数型的增加。对于经典的体硅衬底MOS管,栅极的泄漏电流的增加将引起整个电路的静态功耗的增加,而相对于SOI MOS管结构,栅极泄漏电流将显著的引起管子沟道的电位变化,从而影响器件的阈值电压和整个电路的功能。栅极氧化层厚度减小的另一个效应是MOS管子反型层导电子的丢失和器件跨导的减小[8]。这主要是由于氧化层厚度减小,导致管子反型层的量子化和多晶硅栅极的耗尽。这些都降低了栅极对器件沟道的控制能力。因此栅极氧化层的遂道电流和管子反型层导电子的丢失是栅极氧化层厚度减小的最主要的限制。它们也直接限制了CMOS场效应管尺寸的进一步减小[9]。为了减小这些效应,人们可以采用高介电常数的栅极氧化层和用金属栅极来替代经典的多晶硅栅极等办法来解决。

·最小供电电压

根据MOS场效应管的按比例缩小原理,在保持沟道电场为常数的情况下,电路的供电电压也将按比例缩小。然而,为了维持与最近十年来所开发的系统的兼容性(它们经常需要5 伏的供电电压),半导体制造商已不太愿意进一步的减小电路的工作电压以使得整个电路的功耗与可靠性变得不可控制[6]。在通常,整个电路的功耗Pchip是电路工作功耗Pactive与截止功耗Poff的总和[9]:

CSW是电路结点的总电容,VDD是工作电压,f是开关的时钟频率,Wtotal是所有截止器件的宽度,Ioff是每个器件的截止电流。从(2)至(4)式所指出的那样,减小工作电压是减小功耗的最有效的方法。但减小供电电压不光只是减小了系统功耗同时也削弱了系统工作的可靠性,特别是在器件按比例缩小以提高系统的集成度和工作速度的情况下。

非常不幸,存在一个最小的工作电压。这是由于为了保持器件有较高的工作速度,它的阈值电压Vth应该与供电电压VDD成正比的减小。然而当管子阈值电压减小时,它的截止电流随这个电压值的减小而成指数型增加。由于电流的增加而MOS管的截止功耗也增加。在现代大多数集成电路的设计中,整个电路系统可采纳的截止功耗要求最小阈值电压Vth是在300毫伏左右,这就要求最小供电电压在1伏左右[6]。这显然与大多数已开发的系统不兼容,需要重新来实现,直接导致工作量的大量增加。

·器件连线的分布电阻与分布电容

与器件的按比例缩小原理相反,器件连线的分布电阻和分布电容随连线宽度的减小而增加。因此,这也从电路的工作速度和集成度方面对按比例缩小的CMOS工艺构成一个限制。为了克服连线分布电阻的问题,在几年前,铜连线的工艺被引进。而对于分布电容人们也研究了很多低介电常数的连线与硅基片的绝缘层接构。今天,由于器件连线分布电阻电容在不同器件之间所引起的时间滞后效应一直是现代CMOS工艺发展的主要限制之一。如果可能,一个有潜力的发展是用超导连线。

·新的CMOS场效应管的发展方向

为了更进一步的减小CMOS管的尺寸,人们已经从理论上研究了很多器件结构。而单晶硅被集成在绝缘体上的结构(SOI)是最有发展前途的而且被许多像IBM,MOTOROLA和AMD等大的半导体制造公司所采纳。相对于经典的体硅CMOS 结构,SOI CMOS结构的最大不同是像在图3 所描数的那样,人们在硅晶片中加了一个氧化埋层,也就是一个绝缘层。用这种结构所制造的微处理机比用体硅晶体所制造的同样的微处理机要快20~35%[6]。同时在低功率应用中,由于SOI CMOS工艺的小的寄生电容,也使这种工艺被大量的采纳。

CMOS场效应管的制造工艺极限

·半导体的光刻工艺

这已经被证明现代半导体光刻工艺是有这个能力使人们随器件按比例缩小而制造超大规模集成电路(ULSI)。但是,要用今天的光刻工艺来制造在纳米范围的CMOS场效应管是一个非常重要的待解决问题。经典的光学光刻工艺的精确度由于运用了改进的数字快门镜头和较短波长的激光源已经超过了理论预测的很多倍。现在,最先进的用于大规模制造集成电路的光刻设备是用波长为193纳米的激光源[9]。一些光刻精确度的改进技术,例如可控相位变化技术等,已使我们有能力让图形的精确度在100纳米的这个范围内。这个技术运用的是光学的干涉原理到硅晶片上的图形变化比较大的区域。因此,它不是几何图形独立的,可控相位变化技术不能用于整个芯片中所有器件的制造。对于小于100纳米的范围,经典的光学光刻技术只能用在精度要求不高的地方,而精度要求高的地方,我们必须用X射线光刻或电子束光刻技术[9]。

对于小于100纳米的CMOS工艺,为了获得高精度的MOS管的图形,X射线光刻技术的应用是非常重要的。这个技术应用的主要问题是掩膜版的制造[8]。相对于X射线光刻技术,在小于100纳米的应用范围,另一个有效的光刻技术是用极端紫外光 (EUV)。这个技术用的是一个13纳米波长的反射光。

在近几年的科研领域,纳米结构的图形光刻是用电子束光刻技术。它的光刻精确度是在10纳米的范围。对于电子束光刻技术,它的最大挑战是怎样把它与一般的光刻技术结合起来来加以应用。

·三维立体集成技术

相对于两维平面集成电路,三位立体集成技术已被人们提出,它主要有两点好处:1) 减小了器件之间的连线长度,2) 由于整个芯片尺寸的减小而导致可靠性的提高,进而降低了芯片的造价。三维立体集成技术相对于将来的CMOS工艺是非常具有吸引力的,特别是在系统芯片(SoC)的应用上。运用三维立体集成技术,对于不同的集成电路,人们能够先把它们分别制造,然后再把它们连接起来。三维立体集成技术的主要困难在于:不同电路层的对准与绝缘问题;这些不同层的连接技术;还有在绝缘层上重新集成硅晶体和整个芯片的散热技术问题。

·低介电常数的绝缘介质和超导传输的技术问题

对于不同器件的连接, 人们新进的用化学机械抛光技术(CMP )使铜线代 替铝线。但用铜线代替铝线,好的方面是降低了连线的分布电阻,坏的方面是连线的可靠性变坏[9]。同时,铜连线将不能非常充分的消除整个连线的时间滞后,因为这个滞后是分布电阻和电容的乘积。为了降低连线分布电容,金属连线层的低介电常数绝缘介质的研究是非常重要的。在这方面已经有许多低介电常数的绝缘介质被研究。为了减小连线电阻,高温超导是一个最理想的选择。但依据它的研究现状,在最近的将来把它应用到CMOS场效应管工艺还是有很多困难。

MOS场效应管新的制造工艺的发展方向

为了更进一步减小CMOS场效应管的尺寸以满足现代信息社会的要求,人们需要一些新的制造工艺以克服由于器件尺寸减小而带来的挑战。这包括材料科学的发展和制造设备的革新。在CMOS场效应管新的制造工艺的发展方向的挑战主要集中在以下方面;如何控制工艺的变化;如何改进生产率;如何平衡各种工艺的革新和研究与开发的投资。 总之, 根据人们的预测,半导体工业根据CMOS场效应管按比例缩小原理可以保持它的发展一直到2020年以达到管子的最小沟道长度在10至15纳米这个范围[10]。

结语

CMOS场效应管的工艺发展和它的局限由于它在现代信息社会的重要性是一个非常广范的讨论题目。它的发展还像以前一样继续产生许多博士论文以带来科学与工程的变革。在这篇文章里,我们主要是想简要的讨论当CMOS工艺更近一步发展它的物理参数和制造工艺的限制。

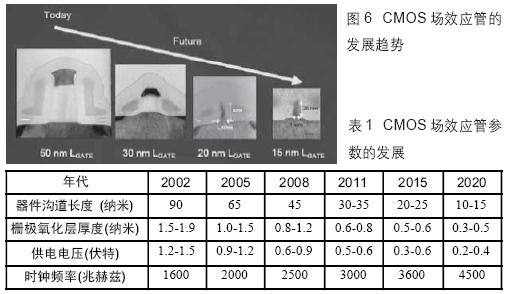

图6和表1 是英特尔公司在21世纪前二十年预测[3][10]:

我们可以看到,CMOS集成电路工艺还将继续按比例缩小一直到10至15纳米这个范围。为了制造十几纳米长的器件,许多非常艰巨的挑战必须被克服。现在人们还不太清楚经典的CMOS场效应管的沟道长度是否可以减小到10纳米以下。因此, 除非有一个革命性的重大突破,否则,以CMOS 集成电路为基础而建立起的半导体工业将完成它光荣的高增长历史使命而变成像钢铁工业和汽车工业一样的传统工业。

参考文献:

1. Neil Weste and Kamran Eshraghian "Principles of CMOS VLSI Design: A Systems Perspective", Addison Wesley Publishing Company, 1985.

2. G E. Moore "Cramming more components onto integrated circuits", Electronics Magazine, Vol. 38, April 19, 1965 pp. 114-117.

3. http://www.intel.com

4. J. D. Meindl "Low power microelectronics: Retrospect and prospect", Proceeding of the IEEE, April 1995, pp. 619-635.

5. E. S. Yang "Microelectronics Devices", McGraw-Hill Inc., 1988

6. T. H. Ning "Silicon Technology Directions in the New Millennium", 2000 38 th Annual International Reliability Physics Symposium.

7. X. Tang, V. De and J. D. Meindl "Intrinsic MOSFET Parameter Fluctuations Due to Random Dopant Placement", IEEE Transaction VLSI Systems, December 1997, pp. 369- 376.

8. H. S. P. Wong, D. J. Frank, P.M. Solomon, C. H. Wann and J.J. Welser "Nanoscale CMOS", Proceedings of the IEEE, April 1999, pp. 537-570.

9. Y. Taur, D.A. Buchanan, W. Chen, D.J.Frank, K.E. Ismai, S.H. Lo, G. A. Sai-Halasz, S. J. Wind and H. S. Wong "CMOS Scaling into the Nanometer Regime", Proceedings of the IEEE, April 1997, pp.486-504.

10. R. Doering and Y. Nishi "Limits of Integrated-Circuit Manufacturing", Proceedings of the IEEE, March 2001, pp. 375-393.

pic相关文章:pic是什么

晶体管相关文章:晶体管工作原理

晶体管相关文章:晶体管原理 离子色谱仪相关文章:离子色谱仪原理

评论