没有ATE生成向量的精密测试(04-100)

—— 没有ATE生成向量的精密测试

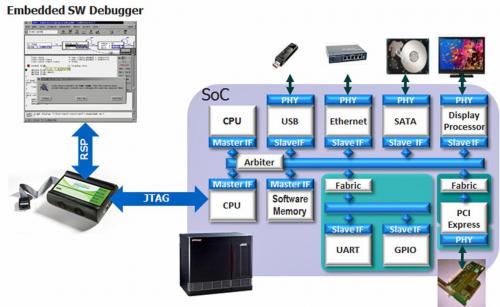

消费类电子产品正在变得更复杂和更快速,因而使得测试成本成为问题。大的和复杂的SoC往往是消费类产品的心脏,不管它们的性能多么先进,其成本必须是低的。

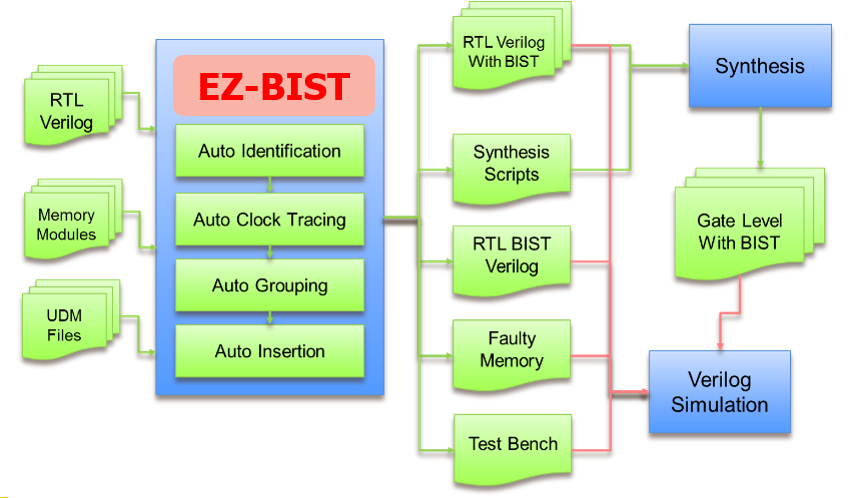

本文引用地址:http://www.amcfsurvey.com/article/81046.htm各种内装自测试(BIST)已应用于测试DUT(被测器件)的内部性能,导致产品较低的生产成本。剩下的主要问题是快速串行接口(如PCI Express,Serial ATA,FibreChannel和Serial RapidIO)的全面测试。这些高速链路在计算、通信和音视频娱乐前进中是不可缺少的。

重视测试成本是一个重要的问题,设计人员已应用BIST技术到串行I/O口中。通常,器件制造商选择用一般的ATE加具有宽范围幅度和定时控制的位图形或在环回配置中BTST产生固定幅度和定时图形。第一种方法是精确和慢速的;第二种方法是快速的,但只在单工作点保证性能。

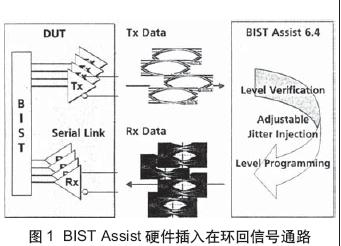

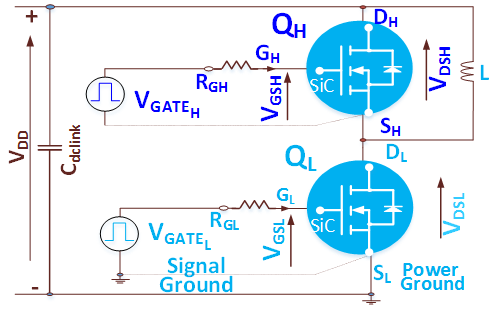

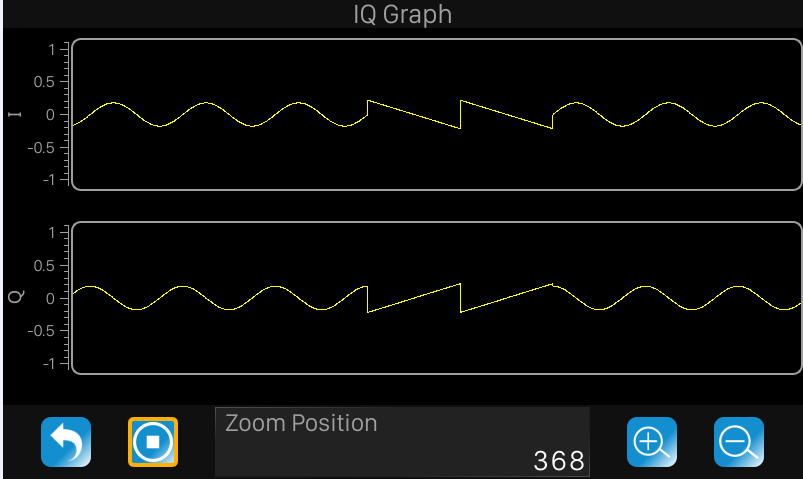

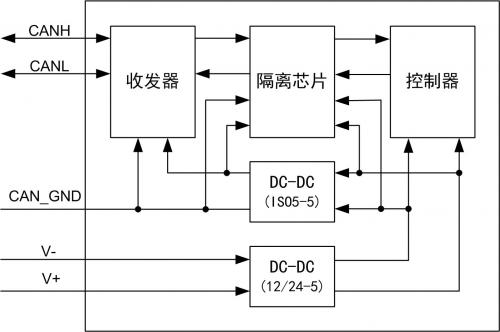

BIST Assist 硬件插入到环路中(见图1)。控制软件支持不同的信号幅度和延迟,这样用所有可允许的值检验其工作。可以注入已知的破坏量(如抖动,偏移和共模信号)确保在最佳条件下正确的DUT行为。图2示出1个通道的详细框图。

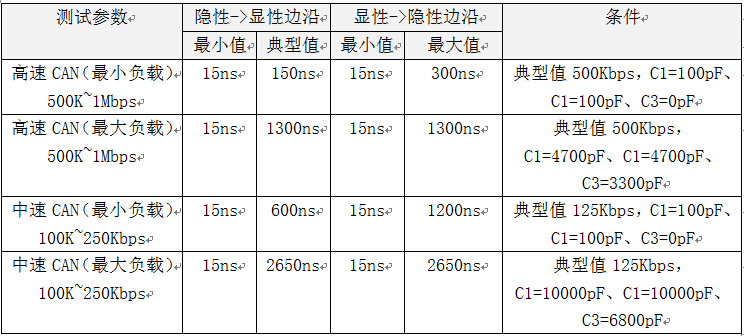

BIST Assist 板上4个分立不同环路的每1个环路的硬件性能指标包括:数据率1.5~6.4Gb/S,100mV输入灵敏度(到100Ω负载)和1.8VPK-PK差分接收器范围。从板上正弦波发生器或430ps的外部信号源在10KHz~100MHz加抖动。

评论