串行/解串器的差分阻抗设计

当今许多手持电子设备都在LCD、照相机和键盘的接口电路中采用串行器/解码器(SerDes)技术。SerDes可以减少穿过铰链或滑动装置的信号数量,从而允许采用新的铰链或滑动装置,并可以降低成本。从并行传输线转换成串行传输线将产生差分阻抗的问题,差分阻抗将严重影响差分信号的完整性,导致LCD屏幕闪烁、射频干扰以及器件的容限问题。本文讨论手持电子设备中高速信号的差分阻抗效应,并讨论如何测量、调试和解决这些问题。

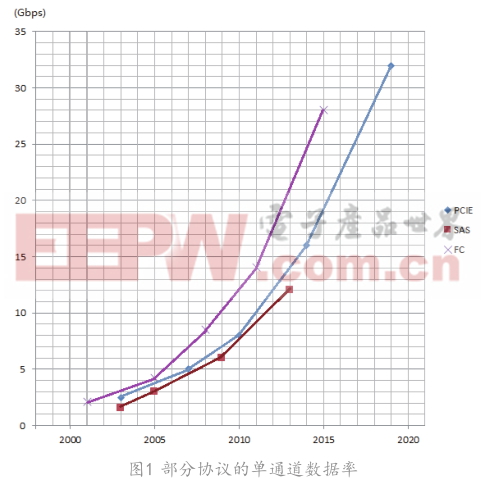

本文引用地址:http://www.amcfsurvey.com/article/80241.htmSerDes器件一般都采用差分阻抗为100Ω的传输线,但在手持设备中实现100Ω传输线非常困难。例如,在翻盖或滑盖手机上,传输线必需经过基带PCB、铰链的柔性PCB、LCD PCB或者软硬复合板。在经过这些介质后仍保持100Ω的差分阻抗是非常困难的。

有许多因素会影响差分阻抗,比如走向宽度、邻近的地线及介电常数。但最主要的影响来自地平面,即一个地平面(微带线)或两个地平面(带状线)以及传输线与地平面之间的距离。这在射频环境中是个大问题,因为这类应用都要求在大多数电子器件表面进行隔离接地,以屏蔽EMI。这种接地会大幅降低传输线的差分阻抗,使其降到50Ω或以下。

低差分阻抗

差分阻抗降低会给信号传输带来许多问题,第一个问题是阻抗失配将导致信号发生反射,其它两个问题则在射频环境下更为突出。较低的差分阻抗意味着传输线呈现更强的电容性,这会给信号传输增加负荷并降低阶跃信号(如时钟信号)的幅度。信号幅度降低会影响无线电系统的RF鲁棒性,例如在GSM手机中,信号幅度降低会严重影响串行数据。GSM接收机的最大发送信号强度一般为32.5dBm,在这个信号强度下,大量的射频信号会耦合到串行线路上。如果SerDes信号的幅度由于传输差分阻抗降低而减小,就会发生数据位错误,导致LCD闪烁。

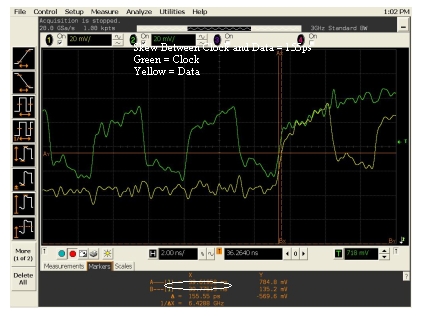

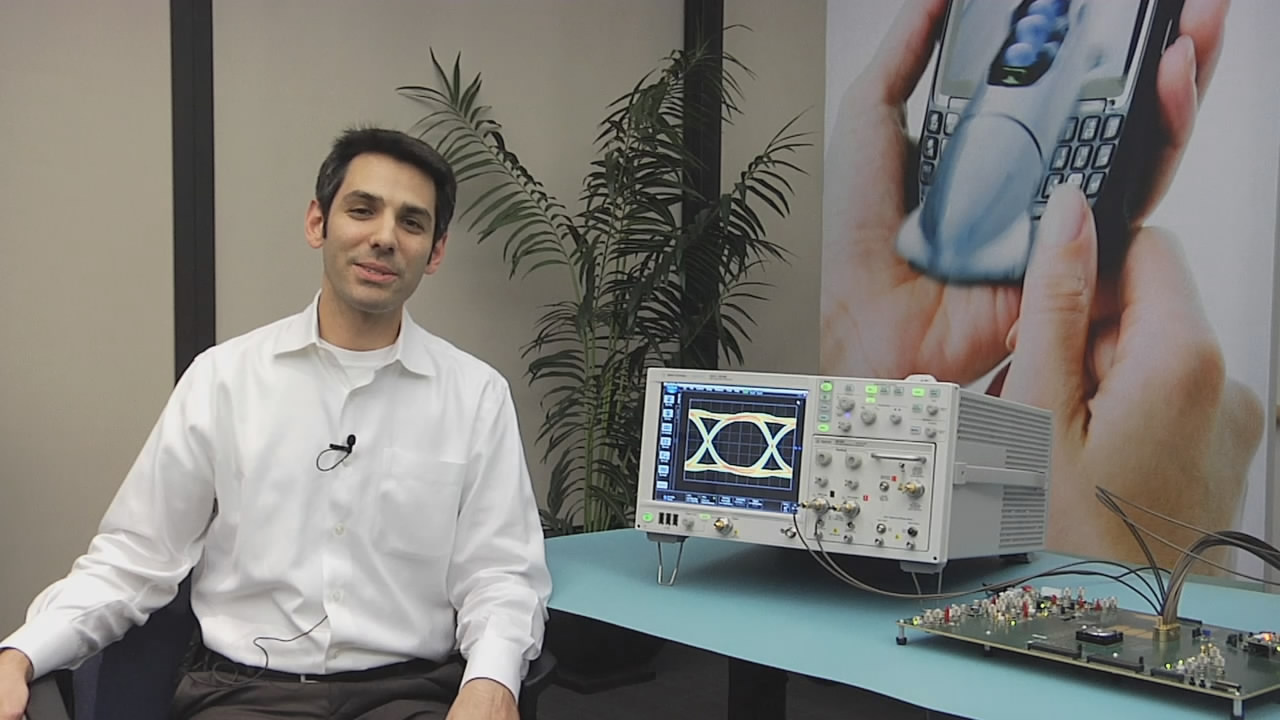

第三个问题是时钟和数据间出现歪斜失真。在图1中,时钟信号始终在跃变,因而其幅度会因差分阻抗降低而降低,但数据并不一定始终在跃变。当有2到3个数据位保持不变时,数据信号幅度就会达到其满幅度。当数据信号跃变时,就会因差分阻抗降低而导致时钟和数据之间的歪斜失真。这看起来问题似乎不大,但典型的SerDes歪斜失真的容限为±150ps,差分阻抗降到39Ω时,歪斜失真就会超出这个容限。此外,时钟和数据间的歪斜失真还会导致数据错误,并降低数据对RF干扰的抵御能力。为确保串行传输方案在射频环境下正常工作,就必须解决差分阻抗降低的问题,并选择歪斜失真容限最大的SerDes器件。

图1:当差分阻抗降到39Ω时,时钟和数据之间出现歪斜失真。

高差分阻抗

差分阻抗降低是因为接地效应过度,阻抗升高则是因为接地效应不足。接地屏蔽并非影响差分阻抗的唯一因素,走线宽度和介电常数也可引起阻抗升高,但接地屏蔽是主要因素。阻抗升高多见于那些无接地屏蔽的线缆(如带状线缆)或者带有气隙的柔性线缆。通常,相对于位于外层的接地屏蔽来说,串行走线位于内层,串行线与接地屏蔽之间的距离对阻抗升高的贡献较大。较低的差分阻抗意味着传输呈现较强的电容性,较高的差分阻抗意味着传输呈现较强的电感性。

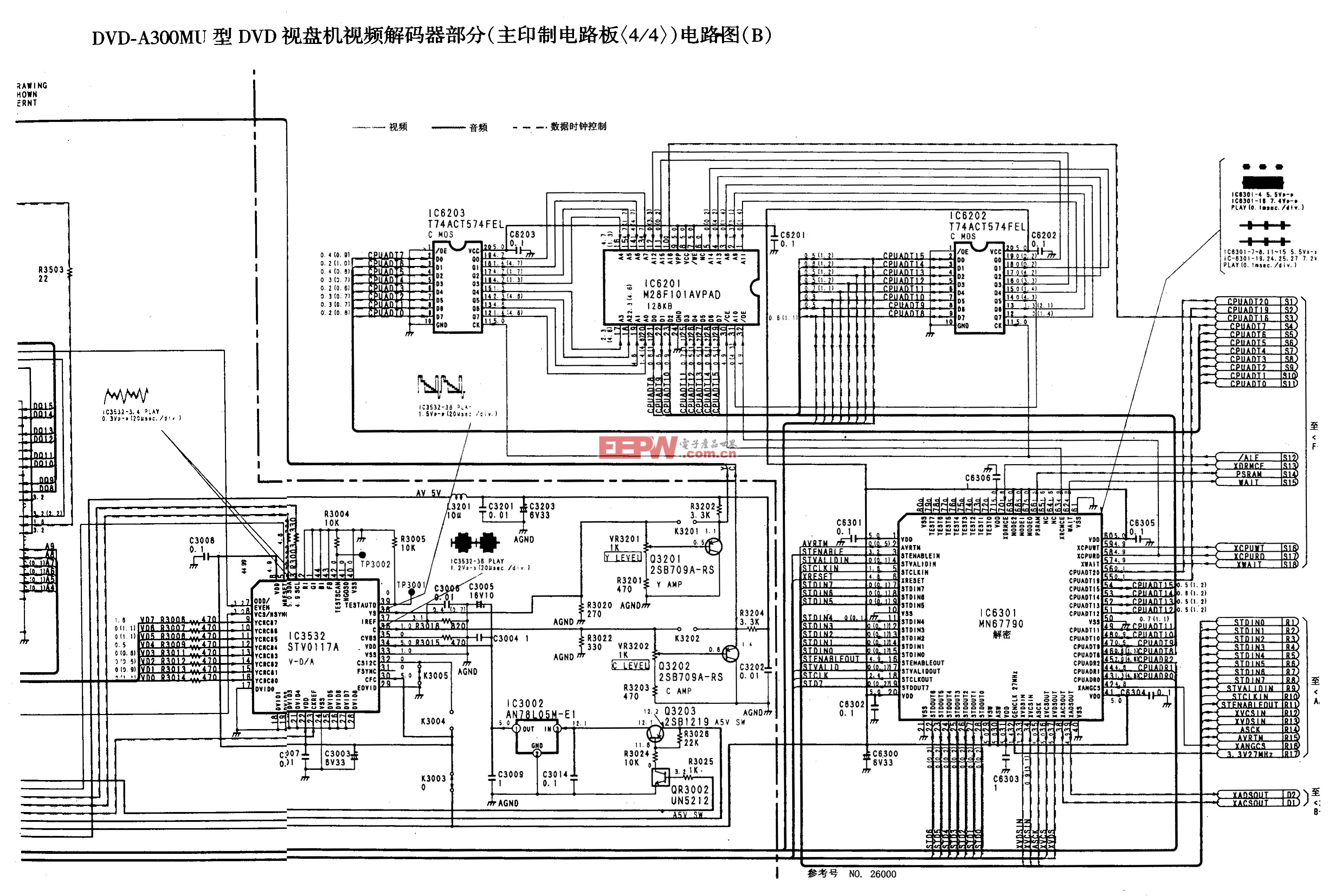

阻抗升高后会带来两个问题。第一个问题是因阻抗失配而产生的信号反射,第二个问题是因阻抗增加而造成过冲和下冲失真(图2)。严重的过冲或下冲失真将使信号超出共模范围,导致数据错误。这种失真也会降低抵御串扰和RF干扰的能力。比如,如果串行信号强度接近共模范围,那么,即使强度不大的串扰也会使串行信号超出共模范围。在射频应用中,导致阻抗升高的最大潜在因素是采用带气隙线缆的设计。

图2:高差分阻抗将导致过冲和下冲失真。

电磁干扰

在解决差分阻抗下降问题的时候,可能需要采用单端接地屏蔽。许多RF工程师都担心这会影响接地隔离的效果,:一是担心高速信号的RF辐射会给电话无线通道带来问题,二是担心高速信号容易受到RF干扰。为解决这些问题,SerDes器件制造商采用差分信号技术来避免反射信号的产生,提高信号抗干扰能力,并努力找到能避开无线电频带的传输频率。接地太多或太少都会引起问题。如前所述,过多的接地会降低串行信号的幅度,削弱信号抗RF干扰的能力,导致数据位错误。接地太少则可能使更强的射频信号耦合到串行信号上。平衡这两个问题的方法是采用单端接地(采用微带线)和网格状接地。采用微带线和网格状接地可使差分阻抗接近100Ω,同时也能达到一定的隔离效果。

设计100Ω差分阻抗的步骤

如果由于接地屏蔽太多而造成差分阻抗降低,或者因接地屏蔽太少而造成差分阻抗增大,那么应该如何设计?什么样的产品能支持这种应用环境?首先,要选择差分阻抗匹配范围大的SerDes器件(比如飞兆半导体的μSerDes器件)。许多串行技术都要求100Ω±10%的匹配容限,但事实上这是不可能实现的。uSerDes技术基于恒流型I/O而不是电压型I/O,并且允许差分阻抗在70到120Ω范围。在PCB或FPCB板设计串行传输线时,使用差分阻抗计算器非常有用。现在市面上已有能结合邻近接地和磁场因素的专业级计算器,可以完成最精确的模拟。如果没有这类设备,也可求助于网络,许多网站都能基于业界已知的一些基本公式来计算差分阻抗。这些公式的效果一般都接近专业计算器,只要不超出它们的使用限度。

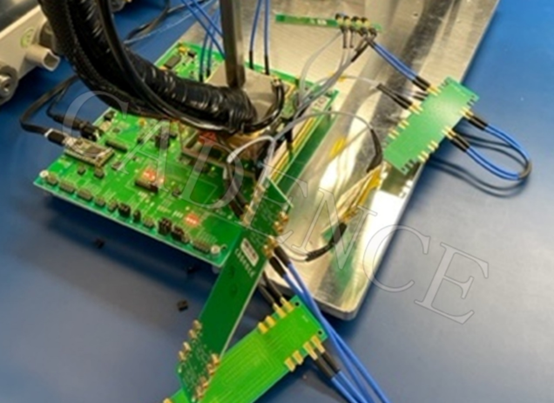

完成板卡和柔性线缆的设计、制造和装配后,建议采用时域反射计(TDR)测量。TDR是一个非常有用的解决差分阻抗问题的测试工具。在测试一对差分线时,TDR发送差分信号到传输线上,并测量阻抗失配引起的反射。做此测试时,最好解决好差分阻抗的降低问题。如前所述,差分阻抗降低一般源于接地屏蔽,解决此问题最直接的方法是检查Gerber文件,找出问题接地点所在。一般最需要注意的区域是PCB上连接器处的内层串行走线,以及带双接地屏蔽的线缆的可动部分。请注意以下几点:内层串行走线的上下层一般都有隔离接地;连接器处的走线难度很大,40条以上的线路都要连接到连接器上,通常会在串行线上下层都进行额外的屏蔽;柔性线缆的活动部分一般都非常薄,串行线上下层的接地会大幅减小差分阻抗。

解决这些问题的第一个保守方法是去除接地屏蔽,或者增加串行线与接地屏蔽之间的距离。如果去除接地屏蔽不可行,可以采用别的方法稍微提高差分阻抗。例如,如果走线宽度原来为4mil,则将其改为3mil,那么差分阻抗将提高约10Ω。另一种可能奏效的方法是使用网格状接地屏蔽,而不是采用实心覆铜。网格状屏蔽有助于将差分阻抗提高约10Ω,同时还能实现屏蔽隔离。

随着越来越多的手持电子设备采用串行传输技术,差分阻抗的问题越来越突出。在PCB和柔性PCB布线之初就找出这些问题非常关键。在信号幅度、抗干扰能力和电磁辐射间进行权衡,就能构建出鲁棒的串行传输解决方案。

评论