基于现场可编程门阵列的数控延时器的设计

l 引言

本文引用地址:http://www.amcfsurvey.com/article/80236.htm利用硬件描述语言结合可编程逻辑器件(PLD)可以极大地方便数字集成电路的设计,本文介绍一种利用VHDL硬件描述语言结合现场可编程门阵列(FPGA)设计的数控延时器,延时器在时钟clk的作用下,从8位数据线输入延时量,到LATCH高电平时锁存数据,可以实现对触发脉冲TRIG的任意量的延时。由于延时范围不同,设计所用到的FPGA的资源也不同,本文详细介绍最大延时量小于触发脉冲周期的情况。该延时器的软件编程和调试均在MuxplusⅡ环境下完成,系统设计选用Altera公司的EPFl0K30AQC208-3,EPCI44l型专用电路,与DSP相结合,应用于雷达目标模拟器的控制部分,实现对目标距离的模拟。

2 设计原理

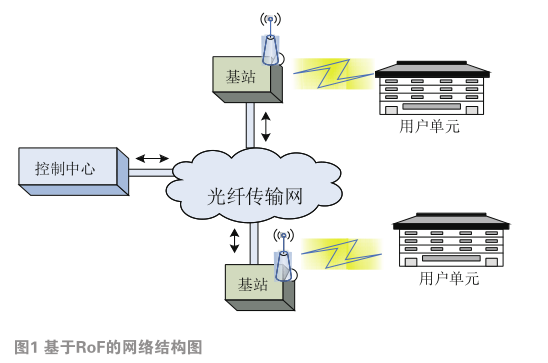

笔者设计的数控延时器采用3个串联计数器来实现。由于在触发脉冲TRIG的上升沿开始延时,使用时钟的上升沿计数,考虑到VHDL对时钟描述的限制,设计采用计数器l产生同步脉冲SYNC,宽度为Tclk,利用SYNC的高电平触发cflag,并在延时结束后cflag清零;计数器2计算延时的长度;计数器3计算所要产生的输出脉冲OUTPUT的脉宽,并在计数结束时对计数器2和计数器3清零。延时器的外部接口电路如图1所示,原理框图如图2所示。整个电路的设计采用同步时钟计数以尽量减少因局部时钟不稳定所产生的毛刺和竞争冒险。

该数控延时器低电平时锁存数据,高电平时改变内部寄存器的数值(与AD9501型数控延时器的数据锁存端电平相反)。一般情况下,触发脉冲与时钟的上升沿是一致的,如果输入的触发脉冲与时钟不一致,则整个电路的延时将产生一定的误差。时序仿真如图3所示,延时量由dlyLH为高电平时数据总线dATA8上的数据决定。

该数控延时器的VHDL硬件描述语言程序如下:

在该程序中,cntl为延时量,cnt2为输出脉冲的宽度,cflag为开始计数的标志,该段程序在触发脉冲的周期大于256xTclk时,最大延时量为256×Tclk,如果触发脉冲周期小于256xTclk,则最大延时量为Tclk-Toutput(Toutput为输出脉冲的宽度)。

事实上,在实际应用中,延时后的输出脉冲与输入的触发脉冲的频率并不相同,譬如在设计雷达目标模拟器时要求延时后产生一连串的7分频时钟,时序如图4所示(延时后产生11个7分频的脉冲,占空比为2:5)。

要产生上述触发脉冲,只需改变计数器2的长度,并在程序中加入case判断语句即可。

3 延时范围讨论

3.1 延时范围小于触发脉冲周期

这种情况只需增加数据输入端的位数,不过一般情况下,数据输入端位数是固定的,这时可以在FPGA的内部定义多位的数据寄存器。以延时范围为224xTclk为例,在FPGA内部定义24位的数据寄存器,并定义3条地址线dlyLHl、dlyLH2和dlyLH3,通过8位数据总线分3次向数据寄存器送数,送数时间应在前一脉冲延时结束之后与下一脉冲到来之前。数据送入寄存器的程序如下:

点击看原图

3.2 延时范围大于触发脉冲周期

这种情况在实际应用中比较广泛,譬如在雷达模拟器的设计中,所模拟的目标的距离范围一般都很大,因而输出延时脉冲的延时量将大于1个触发脉冲周期,这时在考虑到FPGA资源的前提下,可以采用多路延时合并的处理方法。以延时范围小于4个周期为例,具体时序如图5所示。

利用SYNC信号4分频并产生4路分频后的信号。在FPGA内部设计4个延时电路,SYNCl、SYNC2、SYNC3、SYNCA分别作为4个延时电路的触发信号,每个延时电路仿照第一种延时范围的设计方法,输出触发脉冲通过4个或门送到输出端OUTPUT。值得注意的是每个延时电路内部都要定义1个与DATAREG位数相同的数据寄存器,延时数据在延时开始时送入内部寄存器。使用多路延时合并方法最关键的是要产生准确的分频脉冲,如果产生的脉冲有毛刺,或者电路在设计的时候存在冒险,整个延时系统有可能都不能正常工作。

4 延时误差分析

以延时范围小于触发脉冲周期为例,分析固定延时及延时误差。

该延时器在Muxplus Ⅱ环境下从输入时钟Tclk到dlytrig的延时为8.2 ns;产生SYNC的宽度为Tclk。因此在触发脉冲上升沿与时钟信号上升沿对时,该延时电路的固有延时为8.2 ns+2Tclk。但一般情况下,触发脉冲的上升沿与时钟的上升沿并不是一致的,根据二者之间的关系可知,最大延时误差T满足:O

由于该数控延时器使用时钟来计数,因此延时量只能为Tclk的整数倍。如果设计者希望有更精确的延时,可以在设计的基础上外加一片AD9501,该器件的延时可以精确到(Ttotal+Td)×1/28,其中Ttotal是AD9501的总延时,Td是AD9501的固有延时。

5 结束语

本文详细介绍了利用VHDL硬件描述语言结合FPGA设计一种数控延时器的方法,讨论了延时范围,分析了延时误差,该延时器的设计旨在和DSP相结合实现对延时信号的处理。随着EDA技术的飞速发展,使用硬件描述语言设计FPGA是电子设计人员应该掌握的一门技术。同时,将DSP和FPGA技术相结合是进行数字信号处理的一种趋势。

脉冲点火器相关文章:脉冲点火器原理

评论