AT84AD001型ADC在2GHz高速信号采集系统中的应用

1 AT84AD001的主要特点

本文引用地址:http://www.amcfsurvey.com/article/79445.htmAT84AD001是Atmel(代理商:聚兴科技)公司生产的基于BICMOS技术的高速ADC,该器件在一片ADC上集成了两路(I和Q)独立的ADC,具有8 bit转换精度,每个通道具有l GS/s的采样率,在交错模式下双路ADC并行采样可以达到2 GS/s的采样率。AT84AD001内部集成了1:1和1:2的数据多路分离器(DMUX)和LVDS输出缓冲器,可以降低输出数据率,也可以方便地与多种类型的高速FPGA直接相连,实现高速率的数据存储和处理。为补偿由于器件参数离散和传输路径差异所造成的采样时钟时延,该ADC具有采样延时校准功能,可通过片内的数字采样延时调整功能调整两路ADC的采样时间,也可以使用Q路ADC独有的采样延迟微调功能调整Q路的采样时间,使并行采样模式下两路ADC转换保持更高的时序精度。AT84AD001的所有参数设置均通过三线串行接口实现,利用该三线串口可由微处理器对ADC的工作模式进行控制,采用这种结构减少了芯片引脚数和空间体积,并使电路工作参数设置更灵活、简便。AT84AD001可广泛应用于雷达、通讯、仪器以及医疗等领域的高速数据采集过程。

2 外部引脚

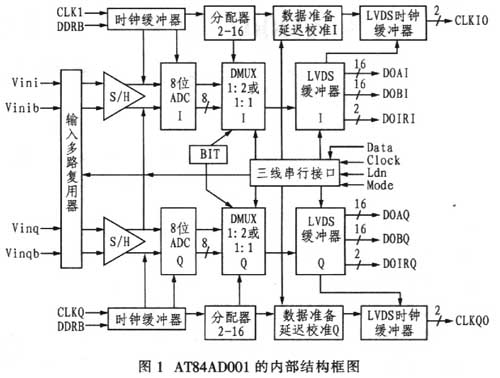

AT84AD00I有144个外部引脚(参见图1)。按性质主要分为模拟、数字两部分。

模拟部分引脚分为模拟电源和模拟输入两类。模拟电源是3.3 V,模拟输入必须配置成差分输入,并且具有500 mVpp的峰峰值。双通道共有两个差分模拟输入端Vinib和Vinqb,若前端信号是单端的,则必须经过一个射频变压器将单端信号变换为差分信号。数字部分包括时钟信输入CLKI和CLKQ、数据输出信号、数据准备信号(CLKIO和CLKQ0)、数据溢出修正位DOIR、三线串口和数字电源。其中电源有3.3 V和2.25 V两种。如图l所示,DDRB是I和Q通道的同步数据准备复位端。Mode、Clock、Data、Ldn分别是三线串口的使能控制位、时钟输入引脚、数据输入引脚、数据输入的起止控制位。DOA(B)I0~7、DOA(B)Q0~7是通道I和Q的差分数据输出端口,1:lDMUX模式时每路ADC使用DOA 8位总线,l:2DMUX模式时使用DOA和DOB 16位总线。DOIRI(N)和DOIRQ(N)是I和Q通道的并行数据差分输出溢出修正位。

3 AT84AD00l的三线串行接口

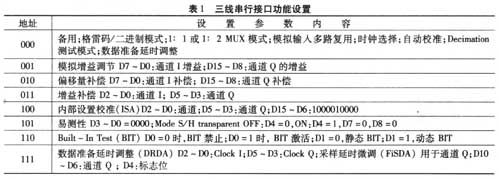

ADC的三线串口是用户可以使用的资源,ADC的所有参数设置均通过三线串口实现,ADC的三线串口主要有3个控制引脚:Data、Clock、Ldn。系统复位后,在每个Clock上升沿1 bit数据被接收。三线接口寄存器地址和设置参数内容如表l所示。串行接口的写入字长为19 bit,其中前3 bit为所要操作的寄存器地址(范围为000-111),后16bit为写入数据,接口的最大时钟频率是50 MHz。可采用多种类型的逻辑单片机作为控制器直接与三线接口相连,通过执行控制程序实现参数设置。ADC具有参数设置模式选择端,如果引脚Mode=1,使用三线串口设置参数,如果引脚Mode=0,上电后进行缺省参数设置,无需外部处理器控制,缺省设置为:双通道工作,使用同一工作时钟CLKI,1:1 DMUX模式,二进制数据输出。

4 AT84AD001的工作模式

为适应不同采样方案的需要,按工作时钟源的不同可将ADC分成三种工作模式:

(1)两个ADC通道使用独立的工作时钟,系统需要为ADC提供两个时钟;

(2)两个ADC通道均使用I通道工作时钟,Q通道的工作时钟与I通道同频同相;

(3)两个ADC通道均使用I通道工作时钟,ADC内部产生一个同频反相的时钟作为Q通道工作时钟。在这种模式下,当两通道输入同一模拟信号时,就可以实现交替式并行采样,ADC的采样速率为输入工作时钟的2倍。

根据两路ADC输入模拟信号的不同,ADC可以分成三种工作模式:

(1)两个ADC通道分别使用独立的模拟输入,整个ADC需要外部输入两个模拟信号;

(2)两个ADC通道均使用I通道模拟输入信号;

(3)两个ADC通道均使用Q通道模拟输入信号。

通常ADC的输出与高速逻辑电路相连,进行数据的存储和处理,根据接收系统处理速率的不同,ADC设置了两种输出工作模式,当DMUX=1:1时,ADC的数据输出率最高为l GHz,双路全部工作时,输出数据宽度为16位;当DMUX=1:2时,ADC的数据输出率最高为500 MHz,双路全部工作时,输出数据宽度为32位,数据输出速率降低了1倍。

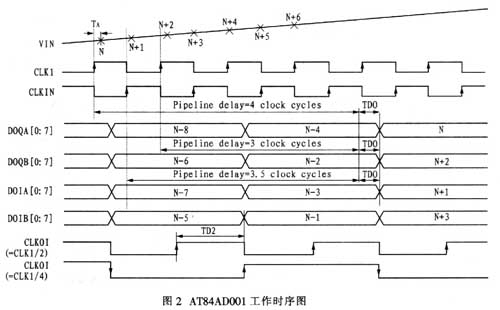

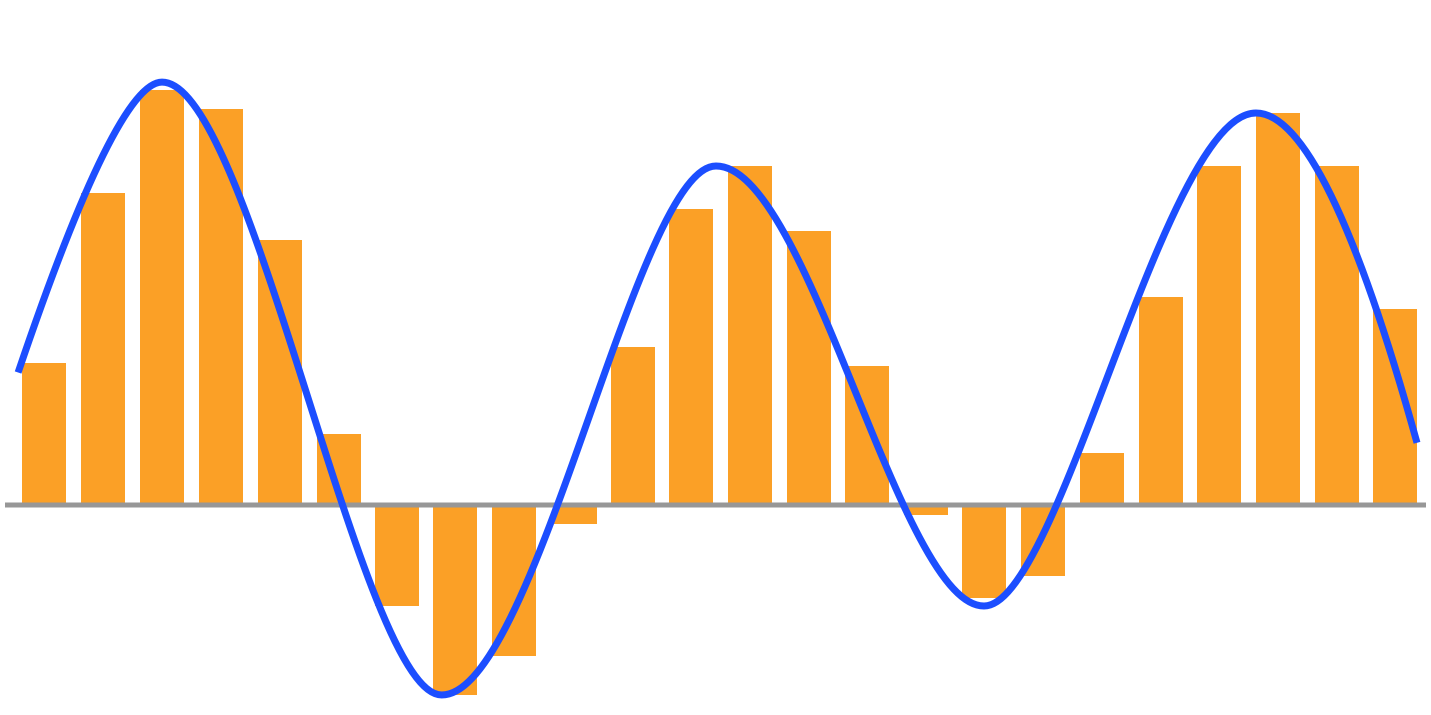

图2为并行交替工作模式下ADC工作时序图,两通道都使用I通道输入模拟信号,外部输入时钟作为I通道工作时钟,Q通道的工作时钟与I通道工作时钟同频反相,DMUX择1:2。

在图2所示的ADC工作时序中,数据输出延迟TDO是一个固定的延时值,总的延时等于固定延时与流水线传输延时之和。在DMUX设置为1:2时,I通道两组数据的流水线传输延时分别为4个时钟周期和3个时钟周期,Q通道则分别为3.5个时钟周期和2.5个时钟周期,这种设计可以使ADC两个通道的转换数据在同一相位输出,有利于接收系统进行同步数据读取。

5 系统设计

AT84AD001在图2所示的工作时序下,输出4路8 bit-500 MS/s LVDS逻辑的数据,在采集系统设计中对与其接口器件的性能要求也较高。Altera公司的Stratix2系列FPGA-EP2S60F1020具有高达84个专用LVDS差分逻辑接收通道,每个LVDS通道数据传输速率最高达640 MS/s。一片EP2S60F1020即可满足接收ADC输出数据和逻辑控制的需要。由于ADC的输出和FPGA的输入均设计为LVDS逻辑标准,因此,ADC可直接与FPGA相连。Stratix2系列FPCA内部具有专门的LVDS处理单元,可实现LVDS逻辑的串/并降速转换,降低速率后的数据可提供给内部DSP处理单元进行处理。Stratix2系列FPGA的另外一个优点是其内部具有专门的高速数字锁相环电路,能够产生可供ADC电路使用的时钟信号。

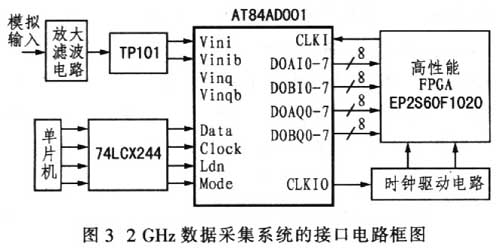

图3所示为基于AT84AD001的2 GHz数据采集系统的接口电路框图。模拟输入信号经过前置放大滤波电路,再经过一个射频变压器TP101将单端信号转换为差分信号,送入AT84AD001的I通道模拟输入端,由于所选的特殊的工作方式,Q通道的模拟输入端无须输入信号。ADC的工作时钟CLKI由FPGA提供,FPGA输入一个频率较低的时钟,经内部数字PLL倍频和逻辑组合产生频率为l GHz的工作时钟,作为ADC的采样时钟CLKI。在图2所示的工作模式下,ADC的数据准备信号CLKIO可以作为系统数据采集和处理的同步时钟,CLKIO为差分LVDS逻辑,速率为250 MS/s,在时钟的上升沿和下降沿均起作用。ADC输出4路8 bit-500MS/s的数据,共占用FPGA的32个LVDS逻辑输入通道。ADC的三线串行接口通过一个AVR系列单片机ATmegal28L进行控制,其中单片机产生的信号逻辑电压为3.3 V,而ADC三线接口逻辑电压为2.25V,因此需要在单片机和ADC之间加一个缓冲器74LCX244进行电平转换。

6 结束语

介绍了采用高速BICMOS技术的AT84AD001型模数转换器,并将其应用在2 GHz数字采集系统中。它的典型三线串口功能简化了ADC的外围电路设计,提高了超高速电路的性能。由AT84AD001及其接口器件EP2S60F1020构成的数据采集系统采样速率达到了2 GS/s,可以应用在现代宽带通信中。随着现代超宽带技术的发展,这种超高速数据采集方案可以用来设计一种全数字化超宽带(UWB)接收器的数据采集系统,以便将软件无线电技术应用于超宽带通信系统中,而高速ADC在全数字化超宽带接收器的设计中起了关键作用。

评论