基于dds的快速跳频频率合成器的设计

跳频通信是扩频通信的一种主要形式。由于其具有抗干扰、抗截获的能力,并能做到频谱资源共享,在当前军事抗干扰通信系统中被广泛应用。跳频通信系统的一项重要参数是频率的跳变速度。它在很多程度上决定了跳频通信系统抗跟踪式干扰的能力,这一点在电子对抗中尤为重要。因此,快速跳频频率合成器的设计就成为跳频通信的关键之一。

目前频率合成主有三种方法:直接模拟合成法、锁相环合成法和直接数字合成法。直接模拟合成法利用倍频(乘法)、分频(除法)、混频(加法与减法)及滤波,从单一或几个参数频率中产生多个所需的频率。该方法频率转换时间快(小于100ns),但是体积大、功耗大,目前已基本不被采用。锁相环合成法通过锁相环完成频率的加、减、乘、除运算。该方法结构简化、便于集成,且频谱纯度高,目前使用比较广泛,但存在高分辨率和快转换速度之间的矛盾,一般只能用于大步进频率合成技术中。直接数字合成(DDS)是近年来迅速发展起来的一种新的频率合成方法。这种方法简单可靠、控制方便,且具有很高的频率分辨率和转换速度,非常适合快速跳频通信的要求。本文将介绍DDS的工作原理,并给出基于DDS的跳频频率合成器的设计。

1 DDS的结构及工作原理

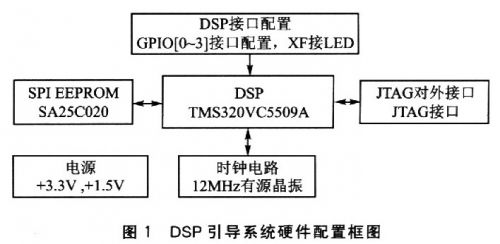

直接数字频率合成是采用数字化技术,通过控制和位的变化速度,直接产生各种不同频率信号的一种频率合成方法。DDS的结构原理图如图1所示,它由相位累加器、正弦ROM表、D/A转换器等组成。参考时钟fr由一个稳定的晶体振荡器产生,用它来同步整个合成器的各个组成部分。相位累加器由N位加法器与N位相位寄存器级联构成,类似于一个简单的加法器。每来一个时钟脉冲,加法器就将频率控制字K与相位寄存器输出的累加相位数据相加,然后把相加后的结果送至相位累加器的数据输入端。相位寄存器就将加法器在上一时钟作用后产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟的作用下继续将相位数据与频率控制字相加。这样,相位累加器在参考时钟的作用下进行线性相位累加。当相位累加器累加满量进,就会产生一次溢出,完成一个周期性的动作,这个周期就合成信号的一个周期,累加器的溢出频率也就是DDS的合成信号频率。

图1 DDS的结构原理图

DDS的工作原理是:在参考时钟fr的控制下,频率控制字K由累加器加以得到相应的相位数据,把此数据作为取样地址,来寻址正弦ROM表进行相位-幅度变换,输出不同的幅度编码;再经过D/A转换器得到相应的阶梯波;最后经低通滤波器对阶梯波进行平滑处理,即可得到由频率控制字决定的连续变化的输出正弦波。DDS的输出频率f0、参考时钟频率fr、相位累加器长度N以及频率控制字K之间的关系为:f0=K×fr/2NDDS的频率分频率为:Δf0=fr/2N由于DDS的最大输出频率受奈斯特抽样定理限制,所以fmax=fr/2。

2 DDS的特点及跳频能力

新一代的直接数字频率合成器采用全数字的方式实现频率合成,与传统的频率合成技术相比,具有以下特点:(1)频率转换快。直接数字频率合成是一个开环系统,无任何反馈环节,其频率转换时间主要由频率控制字状态改变所需的时间及各电路的延时时间所决定,转换时间很短。(2)频率分辨率高、频点数多。DDS输出频率的分辨率和频点数随机位累加器的位数的增长而呈指数增长。分辨率高达μHz。(3)相位连续。DDS在改变频率时只需改变频率控制字(即累加器累加步长),而不需改变原有的累加值,故改变频率时相位是连续的。(4)相位噪声小。DDS的相位噪声主要取决于参考源的相位噪声。(5)控制容易、稳定可靠。衡量跳频频率合成器性能指标的因素有:频率范围、频率分辨率、频率转换时间、频率准确度和稳定度、频谱纯度等。其中,跳频速度和频率点数是决定跳频通信系统性能的主要因素,系统的抗干扰和保密能力随频率点数的增高和跳速的加快而加强。从DDS的特点可以看出,直接数字频率合成器各个性能指标都较高,特别是其频率转换速度,因此它是实现快速跳频频率合成器的最佳选择。

3 基于DDS的跳频频率合成器的设计

下面将给出一种基于DDS的快速跳频频率合成器的设计。

3.1 DDS芯片的选择

现在流行的DDS产品以Analog Devices公司的最多,主要有AD7008、AD9830~AD9835、AD9850~AD9854等十几种芯片,形成从0~120MHz的宽输出频率范围系列。此外,Qualcomm公司也有Q2334、Q2368等产品。该方案使用Analog Devices公司推出的新一代DDS芯片AD9952,该新芯片能以早期DDS十分之一的功耗提供频率高达400MHz的内部时钟。此外,与以往的DDS芯片相比,该芯片还具有以下优点:(1)内部集成14位的D/A转换器。以往DDS芯片的A/D转换器最多为12位。(2)可进行sin(x)/x校正。通过反sin(x)/x函数滤波器对DAC的输入数据进行预均衡,补偿DAC的sin(x)/x函数的起伏特性,使幅特性变得平坦。(3)内有可编程的相位/幅度抖动电路。相位抖动可减小相位截短带来的杂散,而幅度抖动可减小D/A转换器量化误差带来的杂散,因此较好地解决了DDS的杂散问题。

3.2 频率合成方案

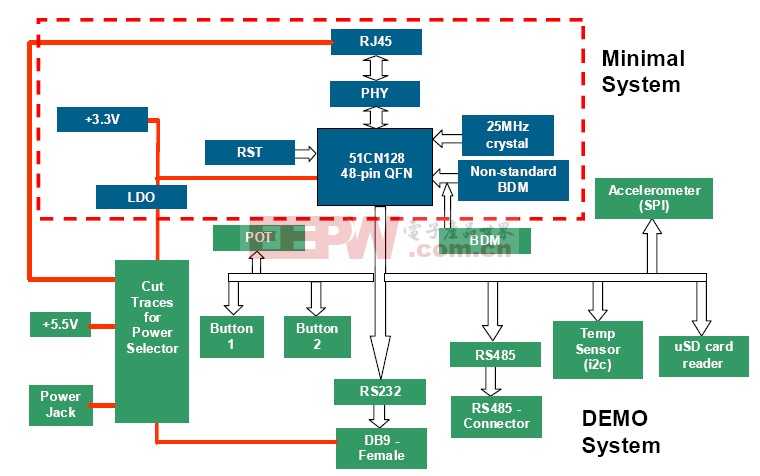

图2是以DDS为核心的跳频频率合成器的结构框图。它主要由DSP、AD9952、时间产生电路、滤波器等组成。DSP采用TI公司的TMS320C54X,负责跳频图案的产生,并控制DDS芯片AD9952的工作。

3.2.1 DDS的时钟AD9952内含振荡电路,因此外加一晶体就可产生系统时钟。也可以不用内部振荡电路而直接引入外部时钟信号。外部时钟信号可以是单端信号或差分信号,并且可以通过配置相应的控制寄存器和控制信号,得到不同的时钟模式。为了减少共模干扰,通常采用差分外部时钟输入方法。本电路中使用高稳定度的有源晶振,然后由差分接收器MC100LVEL16D将晶振输出的单端信号转换为符合AD9952的差分信号。

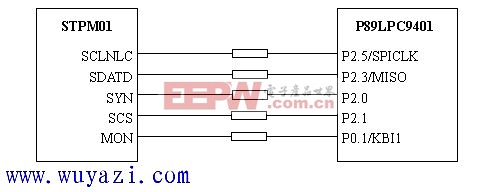

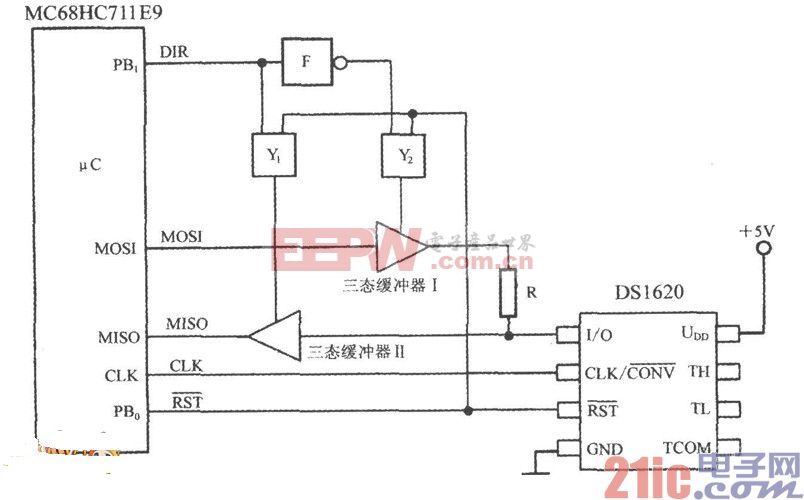

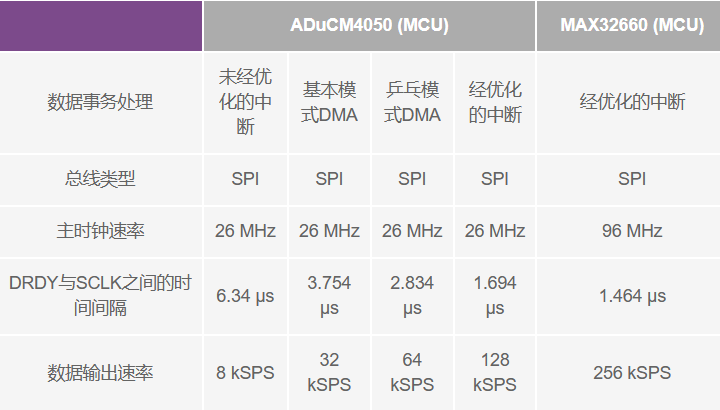

3.2.2 AD9952与DSP的接口设计AD9952与以往的DDS芯片不同,只有串行接口,没有并行接口。AD9952串口是同步串行通信口,易于和工业上的微控制器和微处理器相连;且兼容大多数的步传输格式,可支持SPI协议和Intel 8051 SSR协议。在本方案中就使用了SPI协议。SPI是Motorola公司推出的一种同步串行接口,支持高的数据传输速率,是目前使用比较多的串行总线接口;SPI接口是一种主从式配置,包括1个主设备和1个或者多个从设备。SPI接口有四个信号:串行数据主入从出信号(MISO)、串行数据主出从入信号(MOSI)、串行时钟信号(SCK)、从设备使能信号(SS)。TMS320C54X系列DSP提供一种多通道缓冲串行口(McBSP),通过相关的控制和配置寄存器,可支持多种串行通信方式和协议。McBSP中的传输时钟具有停止模式控制选项,保证了与SPI协议的兼容。McBSP包括6个引脚,分别是串行数据发送信号(DX)、串行数据接收信号(DR)、发送串行时钟信号(CLKX)、接收串行时钟信号(CLKR)、发送帧同步信号(FSX)和接收帧同步信号(FSR)。当McBSP设置为停止方式时,发送和接收在内部实现同步,这使得McBSP可作为SPI的主设备或者从设备。McBSP的发送时钟(CLKX)对应于SPI串行时钟(SCK);发送帧同步信号(FSK)对应于SPI使能信号(SS)。方案中DSP为主设备,AD9952为从设备,二者之间的连接见图2。发送输出信号DX作为MOSI,接AD9952的SDIO;接收输入信号DR作为MISO,接AD9952的SDO。McBSP通过提供串行时钟来控制传输,CLKX只在包传输期间有效,当不进行包传输时,它保持无效。CLKX引脚此时应设置为输出,CLKR引脚在内部与其相连。McBSP的FSX引脚为从设备提供一个使能信号SS,此时FSK引脚设置为输出,在每个包发送时,产生一个帧信号。同时,数据延时参数必须设为1。

3.2.3 滤波器的设计DDS采用数字化技术,最终合成信号是经D/A转换后得到的。其频谱含有很丰富的高次频谱分量,必须将它们滤除,才能得到频谱纯净的正弦波输出,因此要求滤波器的衰减特性要陡直,延迟时间要短。这里采用七阶椭圆函数低通滤波器。

3.2.4 应注意的问题该电路是高速模混合电路,在制作PCB板时,一定要注意数模干扰问题。为此,PCB板一定要使用四层板。在进行电路布局时,将数字部分和模拟部分分开;将电源层分为数字电源和模拟电源;将地层分为数字地和模拟地。每个有源器件的电源都要加去耦电容,并且尽可能地靠近电源输入处以帮助滤除高频噪声。直接数字频率合成具有频率转换速度快、频率分辨率高、输出相位连续和全数字化、易于集成、易于控制等优点,是跳频系统中频率合成器的理想选择。不过,受器件水平的限制,输出信号的频率上限不够高。随着数字集成技术的飞速发展,这一问题将逐渐得到解决。DDS构成的频率合成器必将成为快速跳频通信系统频率合成器的主流。

评论