基于FPGA的数字音频广播信道编码器的实现

摘要:介绍了数字音频广播(DAB)信道编码的原理和关键技术,并应用单片FLEX10K100系列FPGA实现DAB信道编码器。

关键词:数字音频广播(DAB)

信道编码 FPGA

1 数字音频广播(DAB)发射系统及信道编码器

DAB是继调幅和调频广播之后的第三代广播体系。与模拟广播相比它不仅可以提供高质量的声音信号(CD音质),也可以提供数据、图像等多种其他附加服务。它可以保护在高速移动接收时的声音质量,具有很强的抗干扰能力,在同要瓣频带宽度和环境下,DAB可以提供高质量的多种多样的广播节目。

DAB的发射系统主要包括处于节目提供商位置的信源编码器,处于广播台演室位置的复接器和处于发射机内部的COFDM(编码正交频分复用)编码调制器。其中COFDM可分为信道编码、OFDM调和数字上变频。本文主要讨论使用FLEX10K系列FPGA来实现信道编码的功能。

DAB的信道编码部分主要包括能量扩散、卷积编码和删除、时间交织等,输入为来自复接器的ETI(业务群传输接口Ensemble Transport Interface)帧,输出为DAB传输帧。能量扩散的作用是通过对二进制序列的随机化处理使频谱扩散,减少连'0'和连'1'的出现,以保护接收端比特按时恢复。对于信号的传输来说,由于卷积编程引入了大量的冗余比特,因此DAB的信道编码采用删除型的卷积编码。DAB发射机使用时间交织技术来纠正发突发笥的块差错。它按照既定的规则打乱数据排列顺序,使得信道中成块的错误分散在不同帧中,再结合卷积编码的点纠错能力,可以使按收机能够纠正移动传输中经常出现的块差错。

2 FLEX10K系列特点

FLEX10K系列是ALTERA公司生产的一种嵌入式可编程逻辑器件(PLD-Programmable Logic DEVICE)。FLEX(可更改逻辑单元阵列)采用可重构的CMOS SRAM单元,其结构集成了实现通用多功能门阵列所需的全部特征。FLEX10K系列器件容量可达25万门,能够高速度、高性能地将整个数字系统集成于单个器件中。FLEX10K系列的高密度和易于在设计中实现复杂宠函数与存储器,使其可以适应系统设计的要求。

FLEX10K器件可通过ALTERA的MAX PLUS II系统来开发,它具有强大的功能,支持原理图、硬件描述语言(VHDL,AHDL,verilogHDL)等多种输入方式。用FPGA来实现DAB信道编码器,大大简化了系统结构。而且VHDL描述语言的使用缩短了开发时间,增强了系统的可读性,便于后续产品的升级。如果想改变软件设计,只要修改程序、重新编译、下载即可,十分方便。即使要改变硬件设计,也可通过重新分配FPGA管理实现,不需大规模改变原有的硬件。从信道编码器的功能特点看,大部分是比特操作。如果使用DSP或单睡机,每个指令周期只能处理一个字节中的一比特,效率相当低。而FPGA可以对多个比特同时并行操作,大大提高了算是效率。由于FPGA的最高工作频率在100MHZ以上,所以可以通过提高FPGA的工作频率来提高其算是数据的速度。

本设计中所用的FLEX10K100A FPGA是FLEX10K系列中的一种,它的等效门数为10万门,内建24K字节RAM,可用的I/O管脚达到289个,核心电压3.3V,支持5V输入输出。设计中采用原理图和VHDL语言混合输入的方法。

3 用FPGA实现信道编码功能

DAB信道编码技术包括ETI解复接、能量扩散、卷积编码和删除和时间交织。其中ETI解得复接和系统控制由一片DSP ADSP2181来实现,核心部分能量扩散、卷积编码删除时间交织全部由一片FLEX10K100A实现。一个ETI帧中主要包括帧头信息(本帧及帧内各子通道的相关信息)和主业务流数据MST(包括音频数据码流和快速数据通道FIC)。图1是信道编码的硬件实现示意图。来自复接器的码流(ETI)经E1接口板,解出ETI帧,存入输入双口RAM缓冲区。在每帧(24ms)开始时,控制器2181从输入缓冲区读入ETI帧并根据帧头信息计算得一组控制矢量,并将其写回到输入缓冲区,然后启动FPGA。FPGA首先读入控制矢量,然后根据其描述读入ETI帧中MST域的各子通道数据进行能量扩散、卷积编码和删除、时间交织的处理,结果输出到输出缓冲区给OFDM调制器。其中SRAM交织缓冲区是用来存放用于交织的16帧数据的。

信道编码的控制器由ADSP2181实现,控制整个信道编码过程的全部动作,其中主要包括启动编码模块FPGA开始编码、控制FPGA从外部存储器的相应地址读取数据、为编码模块提供进行卷积编码所需的全部参数、为编码后数据提供存储地址等。

下面详细介绍用FPGA实现信道编码的过程。当DSP计算完控制信息后,启动FPGA。FPGA首先读入计算所得控制矢量的前几位帧特征字节,根据这几个字节确定了包括FIC通道在内的子通道个数和输入数据的起始地址,然后分别读入各子通道特征字节,并根据其描述对各子通道进行处理。

3.1 能量扩散

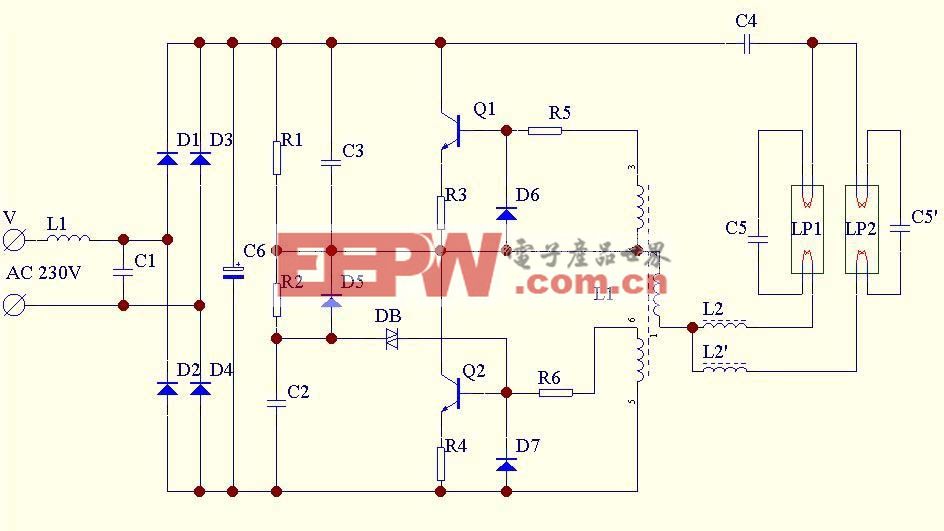

能量扩散采用原理图输入的方法,由9个D触发器和逻辑门实现。在FPGA中,首先按字节读入数据,然后进行并/串转换,将串行输入码流与生成多项式为P(x)=x9+x5+1、初始状态全'1'的伪随机比特序列(PRBS)模二相加(处理的顺序是串行输入的第0比特与PRBS序列的第0比特异或),就得到能量扩散的输出码流。将输出的串行码流送入卷积编码器。图2是能量扩散的实现原理图。

3.2 卷积编码

卷积编码器也是采用原理图输入的方法,如图3所示,通过移位寄存器和其不同抽头的组合来实现的。寄存器的初始化状态为全'0',每输入一个比特会产生4个比特会产生。当有效数据送完时,还要继续送入6个'0'以使全部寄存器清零。若输入长度I的序列 ,则输出序列为

,则输出序列为 。输出序列也可表示为U=(u0,u1,u2,…,u4I+23),其中ui=xR(i/4),Q(i/4)(i=0,1,2,…,4I+23),其中R、Q分别是i/4的余数和商。

。输出序列也可表示为U=(u0,u1,u2,…,u4I+23),其中ui=xR(i/4),Q(i/4)(i=0,1,2,…,4I+23),其中R、Q分别是i/4的余数和商。

3.3 卷积编码的删除

卷积编码输出的前4I个比特被分成连续的比特块,每块128比特。每块又被分为32比特的4个子块,这4个子块使用同一个删除模式,删除模式由PI决定,表1是删除模式表的部分。卷积编码的输出与删除模式表中的删除矢量V相与,剩下的比特压入一个堆栈中。当16比特的堆栈中堆积的比特数>8时,编码器将删除结果按字节输出到16帧长度的交织缓冲区暂存。原始数据的读入、能量扩散、卷积编码和删除是同时进行的。当一个子通道(或FIC)的数据读完时,能量扩散也同时停止,但编码和删除并不停止,还要进行最后24比特的编码和删除,这24比特使用的删除矢量VT=(1100 1100 1100 1100 1100 1100)进行删除。对于有填充字节(Pad)的还要加入填充,最后输出一个字节。 PI是根据输入码流的比特率、保护级(P)和保护方式(EEP/UEP)决定的。在UEP(非平衡差错保护)中,把整个帧的码流(某个子通道)分为3或4块(L1~L4),然后查表即得工程师上应块的PI和填充比特数。表2是此保护级模式表的一部分。对于EEP(平衡差错保护),有A和B两类保护模式表,分别对应输入码率是8Kbits/s的整数倍和32Kbits/s的整数倍,每帧中一个子通道分为2块。一般的删除处理是通过查表进行的,而这里查表的工作由控制器完成,查表结果存在控制矢量字节中。FPGA可直接根据结果编码,有效降低了FPGA的复杂度。

3.4 时间交织

交织开始时,FPGA已经卷积编码删除的结果顺序地写入交织缓冲区,然后按照交织规则乱序地读出数据,完成交织深度为16帧的时间交织。这个缓冲区是一片容量128K字节的SRAM,分为16个8K的块,每块用来存储一帧的卷积编码结果。SRAM的地址组织如图4(括号内是各帧的起始地址)。表3所示的交织规则对应于128K的交织缓冲区,其中r是输入帧的序号,r'是输出帧的序号,i表示比特的序号,R(i/16)表示i除以16的余数,r'(r,i)表示输出第r'帧第I比特应该对应输出第r帧第i比特。Ram_addr表示交织缓冲区此帧的起始地址。

为符号DAB发射系统下级OFDM调制器需要的码元格式,交织后的结果按字节写入输出双口RAM缓冲区时要符合传输帧的数据结构。根据DAB传输帧的要求,这里的输出缓冲区可容纳4个逻辑帧的数据,其片选逻辑也是每96ms变化一次,输出RAM缓冲区内的数据结构如图5。

如上所述,DAB信道编码器可由单片FLEX10K系列FPGA(ADSP2181做控制器)完全实现。这一方法易于实现、工作稳定、速度快、易于升级,可以作为今后集成专用ASIC芯片研制的核心技术基础。

评论