基于IIC1.0的时钟芯片应用程序设计

摘要:在对串行实时时钟芯片X1203内部结构和工作特性作基本介绍的基础上,设计出用单片机的通用I/O口线虚拟I2C总线来实现与时钟芯片的串行接口电路以及利用虚拟I2C总线软件包VIIC设计时钟芯片1203的应用程序。

关键词:单片机 实时时钟 虚拟I2C总线

实时时钟是微机测控系统中的一个重要组成部分。美国Xicor公司推出的串行接口实时时钟芯片X1203提供备用电源输入引脚,使器件能用非可重新充电电池任务用电源。该芯片以其体积小、功耗低、使用简单、接口容易、与单片机连线少为主要特点,同时具有较高的精度,能很好满足微机测控系统的求。下面具体介绍该芯片的内部结构、工作特性、与51系列单片机接口设计实例以及如何利用虚拟I2C总线软件包VIIC来设计实时时钟芯片X1203的应用程序。

1 X1203内部结构和工作特性

X1203是带时钟、日历和2个闹钟报警的实时时钟。双端口时钟和报警寄存器使时钟即使在读写操作期间也能精确地工作,时钟/日历提供了可通过一组寄存器进行控制和读出的功能;时钟使用32.768kHz晶体输入,以秒、分、时、日、星期、月和年为单位跟踪时间,具有闰年校正,并能对小于31天的月自动进行调整;2个闹钟(报警)即中断输出,输出脉冲重复率可以从1次/min~1次/年,支持I2C总线的2线接口,具有400kHz的数据传送速率和内部切换电路的辅助电源输入端,可靠性高,电源电压从2.5~6V实时时钟均能正常工作。

X1203的内部结构如图1所示,由电源控制、振荡器、分频器、时钟控制寄存器(CCR)、控制逻辑电路、移位寄存器等组成。

1.1 X1203的封装形式和引脚说明

X1203有8引脚SOIC和8引脚TSSOP 2种封装形式,引脚排列如图2所示。

SCL:串行时钟引脚,用于使所有数据随时钟同步输入器件和从器件输出。此引脚上的输入缓冲器总是激活的(不选通)。

SDA:串行数据引脚,用于把数据送入器件和从器件送出数据。它具有漏极开路的输出,可以与其它漏极开路或集电极开路输出端进行线“或”。输入缓冲器总是激活(不选通)。漏极开路输出要求使用上拉电阻。

VBACK:备用电源引脚,向器件提供备用电源电压,在VCC电源出现故障时向器件提供电源。

IRQ:中断信号输出引脚。引信号通知处理器,报警已发生并请求动作,是漏极开路的低电平有效输出端。

X1、X2:反向放大器的输入和输出端引脚,可以在X1端接受外部32.768kHz的方波基准或配置为片内振荡器。

电源控制电路由引脚Vcc和引脚VBACK输入,当Vcc<VBACK-0.2V时,电源控制电路切换到VBACK,当VCC超过VBACK时,它将切换回到VCC。{{分页}}

1.2 时钟/控制寄存器(CCR)

时钟/控制寄存器(CCR)分为5个部分:

①报警寄存器0(Alarm0)为8字节,字节地址为0000H~0007H;

②报警寄存器1(Alarm1)为8字节,字节地址为0008H~000FH;

③控制寄存器(Control)为1字节,字节地址为0011H;

④实时时钟(RTC)为8字节,字节地址为0030H~0037H;

⑤状态寄存器(Status)为1字节,字节地址为0003FH;

其中①~③为非易失性的E2PROM,而④、⑤为易失性的SRAM。CCR的映像如表1所列。

表1 CCR映像

| 地址 | 名称 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 范围 |

| 00FH | SR | BAT | AL1 | AL0 | 0 | 0 | RWEL | WEL | RTCF | |

| 0037H | Y2K | 0 | 0 | Y2K21 | Y2K20 | Y2K13 | 0 | 0 | Y2K10 | 19/20 |

| 0036H | DW | 0 | 0 | 0 | 0 | 0 | DY2 | DY1 | DY0 | 0~6 |

| 0035H | YR | Y23 | Y22 | Y21 | Y20 | Y13 | Y12 | Y11 | Y10 | 0~99 |

| 0034H | MO | 0 | 0 | 0 | G20 | G13 | G12 | G11 | G10 | 1~12 |

| 0033H | DT | 0 | 0 | D21 | D20 | D13 | D12 | D11 | D10 | 1~31 |

| 0032H | HR | T24 | 0 | H21 | H20 | H13 | H12 | H11 | H10 | 0~23 |

| 0031H | MN | 0 | M22 | M21 | M20 | M13 | M12 | M11 | M10 | 0~59 |

| 0030H | SC | 0 | S22 | S21 | S20 | S13 | S12 | S11 | S10 | 0~59 |

| 0011H | INT | IM | AL1E | AL0E | 0 | 0 | 0 | 0 | 0 | |

| 000FH | 未用 | |||||||||

| 000EH | DWA1 | EDW1 | 0 | 0 | 0 | 0 | DY2 | DY1 | DY0 | 0~6 |

| 000DH | 未用缺省=RTC年值 | |||||||||

| 000CH | MOA1 | EMO1 | 0 | 0 | A1G20 | A1G13 | A1G12 | A1G11 | A1G10 | 1~12 |

| 000BH | DTA1 | EDT1 | 0 | A1D21 | A1D20 | A1D13 | A1D12 | A1D11 | A1D10 | 0~31 |

| 000AH | HRA1 | EHR1 | 0 | A1H21 | A1H20 | A1H13 | A1H12 | A1H11 | A1H10 | 0~23 |

| 0009H | MNA1 | EMN1 | A1M22 | A1M21 | A1M20 | A1M13 | A1M12 | A1M11 | A1M10 | 0~59 |

| 0008H | SCA1 | ESC1 | A1S22 | A1S21 | A1S20 | A1S13 | A1S12 | A1S11 | A1S10 | 0~59 |

| 0007H | 未用 | |||||||||

| 0006H | DWA0 | EDW0 | 0 | 0 | 0 | 0 | DY2 | DY1 | DY0 | 0~6 |

| 0005H | 未用缺省=RTC年值 | |||||||||

| 0004H | MOA0 | EMO0 | 0 | 0 | A0G20 | A0G13 | A0G12 | A0G11 | A0G10 | 1~12 |

| 0003H | DTA0 | EDT0 | 0 | A0D21 | A0D20 | A0D13 | A0D12 | A0D11 | A0D10 | 0~31 |

| 0002H | HRA0 | EHR0 | 0 | A0H21 | A0H20 | A0H13 | A0H12 | A0H11 | A0H10 | 0~23 |

| 0001H | MNA0 | EMN0 | A0M22 | A0M21 | A0M20 | A0M13 | A0M12 | A0M11 | A0H10 | 0~59 |

| 0000H | SCA0 | ESC0 | A0S22 | A0S21 | A0S20 | A0S13 | A0S12 | A0S11 | A0S10 | 0~59 |

实时时钟(RTC)使用外部32.768kHz石英晶体来保持年、月、日、时、分和秒的精确的内部表示。RTC具有闰年校正和世纪字节。上电后,直到至少有1字节写入RTC寄存器时,时钟才开始计数。启动读命令并指定对应于实时时钟(RTC)寄存器的地址可以读RTC,也可以通过写RTC寄存器来设置时间和日期。2个报警寄存器,其内容模仿RTC的内容,只是增加了使能位并去除了24小时时间选择位。通过使能位和实时寄存器的设置,可以确定报警时间。

控制寄存器中位IM为方式控制位。

①IM=0(正常方式)。RTC与Alarm0寄存器设置的内容匹配时,将自动置位状态寄存器的AL0位。如果控制寄存器的AL0E位也为“1”,则输出IRQ信号将变为有效;如果AL0E为“0”,则AL0位被置位,IRQ信号保持不变。RTC与Alarm1寄存器设置的内容匹配时自动置位AL1位。如果AL1E也为“1”,则输出IRQ信号将变为有效;如果AL1E为“0”,则AL1位被复位,IRQ信号保持不变。

②IM=1(脉冲中断方式)。此方式不使用位AL0E和AL1E,Alarm1的工作如前,RTC与Alarm1寄存器设置的内容匹配时将自动置位AL1位,机必须通过查询AL1位以决定是否发生了报警。Alarm0提供输出响应,RTC与Alarm0寄存器设置的内容匹配时,输出IRQ脉冲1次,脉冲宽度约为30ms。所有的Alarm0寄存器使能选项均可使用,从而实现非常灵活的长时间循环触发器。

1.3 串行通信接口

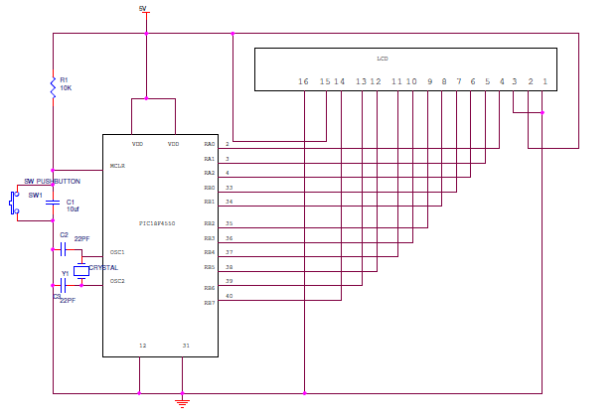

X1203支持I2C总线接口。I2C总线是一个十分完善的多主系统总线,总线上可以挂接多个MCU,因此有4种工作方式:主发送、主接收、从发送、从接收。 下面介绍的单个MCU系统,只用到I2C总线的主方式,即主发送与主接收。目前,带有I2C总线接口的MCU只有少数厂家的个别产品,运用单片机的通用I/O口来虚拟I2C总线接口,可以很好地解决与X01203的接口问题。图3为X1203与51系列单片机的接口。X1203的SCL为串行移位时钟输入,P3.6与SCL相连以产生模拟时钟信号;SDA为串行数据输入输出,P2.7与SDA相连以实现主器件51系列单片机与从器件X1203的数据通信。

下面介绍的单个MCU系统,只用到I2C总线的主方式,即主发送与主接收。目前,带有I2C总线接口的MCU只有少数厂家的个别产品,运用单片机的通用I/O口来虚拟I2C总线接口,可以很好地解决与X01203的接口问题。图3为X1203与51系列单片机的接口。X1203的SCL为串行移位时钟输入,P3.6与SCL相连以产生模拟时钟信号;SDA为串行数据输入输出,P2.7与SDA相连以实现主器件51系列单片机与从器件X1203的数据通信。

51系列单片机对X1203有读写两种操作。写操作包括字节写和页写(1次写8字节连续地址单元),读操作包括当前地址读、随机地址读和顺序读。具体格式如图4所示。顺序读以当前地址读或随机地址读启动,但主器件接收到第1个数据字节后不是结束读周期,而是以应答做出响应。这时读操作的地址计数器自动增量,允许在1次操作期间内顺序读出整个存储的内容。{{分页}}

2 运用虚拟I2C总线软件包VIIC设计时钟芯片X1203的应用程序

由于I2C总线协议的复杂性和操作管理的特殊性,在扩展I2C外围器件时,如果还要在了解I2C总线协议、操作原理的基础上,采用直接方式进行I2C总线外围器件的应用程序设计,就会使得I2C总线应用程序的设计难度很大,也使I2C总线推广应用较慢。因此,迫切需要推出I2C总线的应用软件平台,使大家不必了解I2C总线就能设计I2C总线应用程序。下面介绍如何运用虚拟I2C总线软件包VIIC 1.0来设计时钟芯片X1203的应用程序。

软件包VIIC实现非介入性操作,接口界面是软件包应用时唯一的触及面。VIIC1.0的接口界面为数据读写子程序RDNBYT/WRNBYT,因此RDNBYT/WRNBYT的调用操作命令,以及满足调用操作的初始化操作3的条命令为VIIC的应用界面,即:

MOV SLA,#SLAR/SLAW ;总线上节点寻址并确定传送方向

MOV NUMBYT,#N ;确定传送字节数N

LCALL RDNBYT/WRNBYT; 读/写操作调用

2.1 设定时钟芯片当前值

将时钟芯片当前值设定为2002、3、20、星期三、18:28:38

①将VIIC1.0装入程序存储器中。

②根据硬件电路及资源分配,将VIIC1.0中的符号单元赋值如下:

VSDA EQU P3.7 ;用P3.7虚拟SDA

VSCL EQU P3.6 ;用P3.6虚拟SCL

SLA EQU 60H ;60H为寻址字节存放单元

NUMBYT EQU 61H ;61H为传送字节数据存放单元

MTD EQU 40H ;40H为发送缓冲区首地址

MRT EQU 50H ;50H为接收缓冲区首地址

③设定时钟芯片当前值子程序设计。设时钟芯片当前值设定子程序名为SJSD。SJSD的程序清单如下:

VSDA EQU P3.7

VSCL EQU P3.6

SLA EQU 60H

NUMBYT EQU 61H

MTD EQU 40H

SJSD:MOV 40H,#00H ;将状态寄存器的高位地址、

MOV 41H,#3FH ;低位地址以及要写入状态

MOV 42H,#02H ;寄存器的值依次装入发送缓冲区

MOV SLA,#0

评论