基于DM642的嵌入式网络视频服务器的设计

——

[关键词]DSP; 网络 ;视频服务器

引言

目前的安防监控领域的主流产品是DVR(数字硬盘录像机),它的主要特点是适合监控点集中的局域监控应用。但是,随着对于远程分布式监控需求的增长,嵌入式网络视频服务器以其可靠性高,组网方便等优点越来越受到安防领域厂商和客户的重视。视频服务器的解决方案有多种选择,但是市场产品的主流一般选择两种方案:(1)CPU+ASIC。该方案选择以ARM为核的CPU和专用媒体处理芯片搭建。优点是开发时间相对较短,但由于采用ASIC,灵活性较差,产品一旦定型,很难更改。(2)采用面向媒体处理的专用DSP。其开发时间不长,优点是由于算法是软件代码,所以可以不断对产品性能进行升级,重复开发成本较低。基于以上几点,本系统采用第二种方案设计。

一.系统的硬件设计。

视频服务器最主要的功能是完成图像和声音的采集、压缩及传输的功能。视频服务器用到的核心技术一般包括视频压缩算法,音频压缩算法,网络传输协议。目前市场上的主流技术主要是MPEG4或H26x视频压缩算法、AAC音频压缩算法、G.72x语音压缩算法(或AAC音频压缩算法),TCP/IP协议等。DM642是TI公司推出的一款针对多媒体处理领域应用的DSP,它是在C64x的基础上,增加了很多外围设备和接口。该DSP为548脚BGA封装,高度集成化。主要外围设备包括:三个可配置的视频接口,可以和视频输入,输出或传输流输入无缝连接。VCXO内插控制端口(VIC)10/100Mbps以太网口(EMAC)。数据管理输入输出模块(MDI0)。多通道音频串行端口(McASP)。I2C总线模块。两个多通道有缓存的串口(McBSPs)。三个32-bit通用定时器。用户可配置的16-bit或32-bit的主端口接口(HPI16/HPI32)。6Mhz32-bit的PCI接口。通用I/0端口((GPIO)。64-bit的外部存储单元接口,支持和同步或异步存储单元的连接。

系统硬件框图如下:

本系统设计3路视频端口,2路板上解码器和1路板上编码器,32Mbytes同步DRAM 通过FPGA的OSD 4Mbytes Flash memory ,10/100以太网端口通过FPGA内寄存器执行的板卡软件配置导入加载选项配置。DSP芯片通过64bit的EMIF接口或8/16bit的3路视频接口连接板上外围设备。SDRAM、Flash、FPGA和UART每一个设备占用其中的一个接口。EMIF接口也连接扩展背板接口,扩展背板接口用来连接背板。 板上的视频解码器和编码器连接到视频端口和扩展连接器上。母板上的2个编码器和1个解码器都符合标准规范。McASP可以通过软件重新设定成为一个扩展接口。可编程逻辑门阵列又被称为FPGA,用来执行板上组合在一起的逻辑程序。FPGA有基于软件用户端口的寄存器,用户可以通过读写这个寄存器来配置板卡。

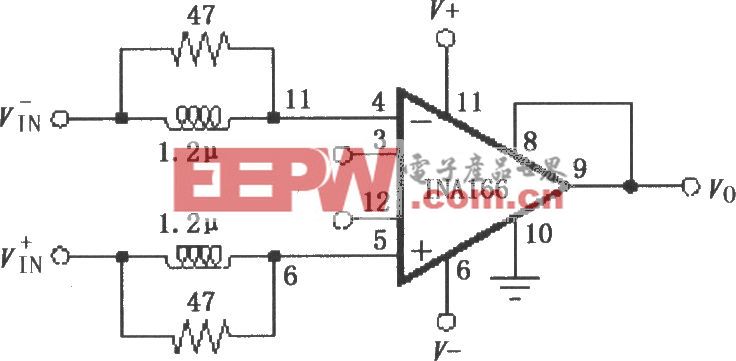

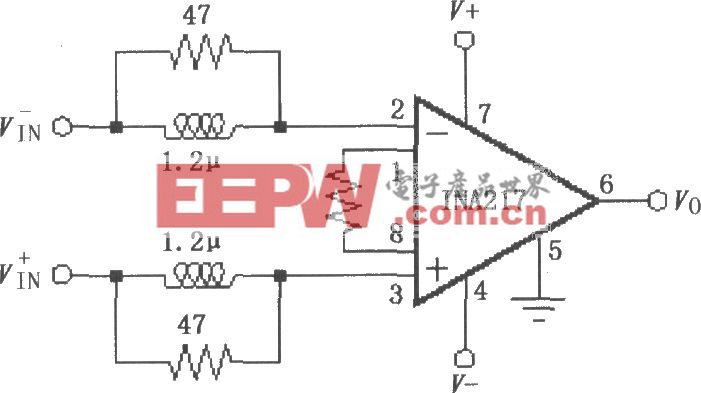

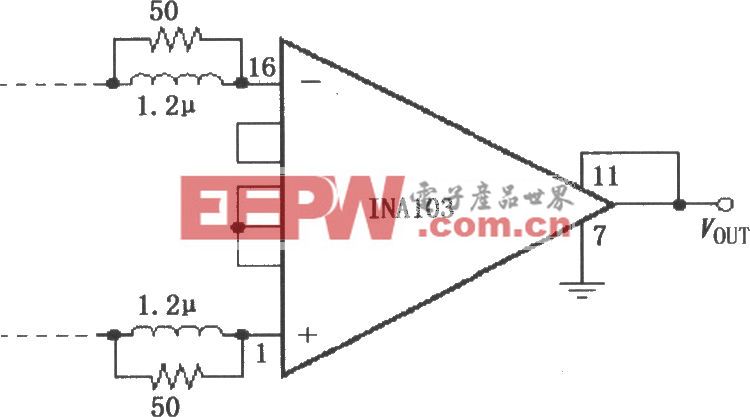

系统的硬件设计主要有以下几个部分。(1)存储器映射。C64xx系列DSP有大量的字节可设定的地址空间。程序代码和数据可被存储在统一标准的32bit地址空间的任何位置。 默认状态下,内部的寄存器从0x00000000地址空间开始存储。一小部分存储器可由软件重新映射为L2高速缓存,而不是固定的RAM。 EMIF(外部寄存器端口)有4个独立的可设定地址的区域,称为芯片使能空间(CE0-CE3)。当Flash、UART和FPGA映射到CE1时,SDRAM占据CE0。背板使用CE2和CE3。CE3的一部分被配置给OSD功能的同步操作和扩展的FPGA中的其他同步寄存器操作。(2)EMIF端口。本系统设计一个64bit长的外部存储器端口。将地址空间分割成了四个芯片使能区,允许对地址空间进行8bit、16bit、32bit和64bit的同步或不同步的存取。DM642板使用芯片使能区CE0、CE1和CE3。CE0被发送给64bit的SDRAM总线。CE1被8bit的Flash、UART和FPGA功能使用。CE3被设置成同步功能。CE2和CE3都被发送给背板接口连接器。 (3)SDRAM寄存器端口。本系统设计在CE0空间连接了64bit的SDRAM总线。这32兆的SDRAM空间用来存储程序、数据和视频信息。总线由外部PLL驱动设备控制,运行在133MHz的最佳运行状态。SDRAM的刷新由DM642自动控制。 EMIF使用的PLL被称为ICS512,PLL的输入时钟是25MHz。DM642可以配置EMIF时钟的原始值。ECLKIN针脚一般为默认值,但其也可通过分频CPU时钟,来控制EMIF的时钟频率。在复位时,通过对ECLKINSEL0和ECLKINSEL1针脚的操作进行设置,其与EA19和EA20针脚共同分享EMIF的地址空间。 (4) Flash寄存器接口 本系统设计4M的Flash,映射在CE1空间的低位。Flash寄存器主要被用来导入装载和存储FPGA的配置信息。DM642评估板的CE1空间被配置成8bit,Flash寄存器也是8bit。由于CE1的可利用地址空间小于Flash的空间,所以利用FPGA来产生3个扩展页。这些扩展的线形地址通过FPGA的Flash的基础寄存器进行定义地址,复位后默认是000。(5)UATR接口。 双重的UART寄存器被映射在DM642的CE1空间的高位,随同FPGA异步寄存器一起。每一个UART,A和B产生8位的地址。本系统设计将CE1空间配置成8位存取。(6)FPGA异步寄存器端口 。FPGA有10个定位在CE1空间高位的异步存储寄存器。这些寄存器实现的各种功能由于篇幅所限不再详叙。FPGA同步寄存器端口 FPGA在CE3地址空间开设同步寄存器。这些寄存器主要实现OSD功能和一些评估板连接(7)EMIF缓冲器/解码器控制 。EMIF缓冲器和解码器的功能通过GAL16LV8D普通逻辑数组驱动器实现,U15。驱动器可以对Flash进行简单的解码处理,UART与缓冲器共同控制CE1、CE2和CE3。(8) 视频端口/McASP端口 。本系统设计有3个板上视频端口,这些端口可以根据可选择性功能,进行再分类,例如端口0和端口1的McASP和SPDIF功能。DM642使用所有的三个视频端口,视频端口0和视频端口1被用作输入端口,视频端口2用作显示端口。在标准配置中,视频端口0和视频端口1根据使用在McASP功能下进行再分类,连接到TLV320AIC23立体声编解码器或连接到SPDIF输出接口J9。 (9)视频解码器端口 。本系统设计可再分的视频端口0和视频端口1被用作捕获输入端口,命名为捕获端口1和捕获端口2。这些端口连接到SAA7115H解码器。视频端口贯穿CBT开关,所以他们为了背板的使用可以被选择性的禁止。另一半的端口被连接到板上的McASP端口。捕获端口1通过一个RCA类型的视频插座J15和一个4针的低噪声S-Video接口J16,连接到视频源。输入的必须是合成的视频源,例如DVD Player或视频相机。SAA7115H是可通过DM642的I2C总线进行编程的,并且可以连接所有的主要合成视频标准,例如NTSC,PAL和SECAM,这些都可以通过解码器的内部寄存器进行适当的编程。(10) 视频编码器端口 。本系统设计视频端口2被用来驱动视频编码器。它通过FPGA U8发送,以实现高级功能,例如OSD。但它在默认方式下是直接通过视频,连接到SAA7105视频编码器。这个编码器可以进行RGB、HD合成视频,NTSC/PAL复合视频的编码,也可对依靠SAA7105内部寄存器进行编程的S-Video进行编码。SAA7105的内部编程寄存器通过DM642的I2C总线进行配置。 编码器连接到合成的或RGB显示单元。通过标准的RCA插座J2、J3和J4提供RGB图像。J3的绿色输出也可以被用于接口到合成显示单元。4针的低噪声S-VideoJ1也可用。15针的高密度DB接口允许系统驱动VGA种类的监视器。本系统设计高清晰TV输出,但要求更换一些支持HDTV的特殊过滤器。(11)FPGA视频功能 。本系统设计使用Xilinx XC2S300E系列FPGA来实现增强视频功能和其他的一些连带功能。默认模式下,FPGA通过DM642的视频端口2输出视频到Phillips SAA7105视频编码器。对于HDTV,FPGA提供增强的时钟;对于OSD功能,FPGA提供了FIFOs,将视频端口2的数据与FIFOs端口的数据进行混合。FPGA的FIFOs在通过CE3空间的同步模式下,通过DM642的EMIF进行存取。(12)以太网端口。在独立的模式下,DM642的以太网MAC被自动选择,并通过CBT发送给PHY。本系统设计使用的是Intel LXT971 PHY。10/100Mbit的端口被隔离,输出至RJ-45标准的以太网接口,J8。PHY直接连接到DM642。在制作过程中,以太网的地址存储在I2C的连续ROM中。 RJ-45接口具有2个指示灯,使它成为一个完整的端口。2个指示灯分别是绿灯和黄灯,用来指示以太网的连接状态。绿灯亮,指示已连接,绿灯一闪一闪,指示连接正在活动;黄灯亮,指示满双方模式。

二.系统的软件设计。

1.数据流程。(1)输入设备提供的一帧图象被采集到输入缓存,由YUV 4:2:2 格式进行重抽样变为YUV 4:2:0 格式。(2)图象数据由输入任务模块通过一个SCOM序列提供给处理模块。

(3)提供图象数据给JPEG 编码库程序,动态检测即与以前图象作比较,动态部分被压缩成JPEG 图象并通过SCOM 消息发送到网络任务模块。(4)网络任务模块建立JPEG 副本,当网上有一个对等端点连接到网络并申请“记录”,网络任务模块发送这些图象到对等端点。(5)如果网上有一个对等端点请求“回放”连接,网络任务模块将从那个对等端点接收新的JPEG 图象,并发送原始和更新的图象到处理任务模块,消息通过SCOM 序列发送。解码产生的YUV 4:2:0 格式的图象被重新采样成YUV 4:2:2 格式的图象。(6)JPEG 图象被作为解码器的输入,解码的图象通过SCOM 序列进行传输到输出任务模块。(7)输出任务模块转换YUV 4:2:0 格式的解码图象成YUV 4:2:2 格式图象并送交显示。显示设备显示输出的图象。2.数据流图。

3.程序流程。

(1)实验程序采用RF-5来整合JPEG 的编码、解码库。程序使用了6 个任务模块结构。其中4 个任务上图中已描述。第5 个任务是一个控制任务,它使用一个邮箱发送消息给处理任务模块。处理任务模块从邮箱接收消息,并根据消息中指定的图象质量调节图象帧率。第6 个任务模块是网络初始化模块,它由CDB 文件定义处理网络环境的初始化。当网络准备好后,上图中的网络任务模块就被建立。在进入DSP/BIOS 的调度程序之前,程序初始化了多个要使用的模块。包括:

①处理器和系统板的初始化:初始化BIOS 环境和CSL,设置使用128K 的二级高速缓存,设置二级高速缓存可映射到EMIF 的CE0 和CE1 空间,设置DMA 优先级序列长度取最大值,设置二级高速缓存的请求优先级最高,DMA 管理器用内部的和扩展堆初始化。

②RF-5 模块的初始化:系统初始化RF-5 的通道模块,系统初始化RF-5 框架中用于内部单元通讯和传递消息的ICC 和SCOM 模块,各通道建立在内部的和扩展的堆上。

③建立摄入和显示通道:建立和启动一个摄入通道的实例。

(2)在完成初始化工作之后,系统进入DSP/BIOS 调度程序管理下的6 个任务系统。6 个任务通过RF-5 的SCOM 模块互相发送消息。以下是这6 个任务:(A)输入任务。输入任务从输入设备驱动程序获得视频图象。它使用驱动程序提供的FVID_exchange调用从输入设备获得一帧最新视频图象。获得的图象是YUV 4:2:2 格式的,它被重采样成YUV 4:2:0。输入任务接着发送消息到处理任务,消息中包含图象数据指针。接着等待处理任务发送来的消息以继续处理。(B)处理任务。处理任务包含两个单元。第一个单元是一个JPEG 编码单元,它接受YUV 4:2:0 格式的图象,产生用户定制压缩质量的JPEG 图象。第二个单元是一个JPEG 解码单元,它接收JPEG 压缩图象并生成解压缩图象。解码的图象格式是YUV 4:2:0 的。首先,如果激活标注,则处理任务模块在输入的图象上加注时间码。然后图象被传输给编码算法单元。当JPEG 图象生成后,原始图象将进行动态检测,方法是在固定网格点上进行象素比较。JPEG 图象同动态检测结果都传输给网络任务模块供后续处理。当网络任务模块完成处理后,它将返回一个JPEG 图象给处理任务模块供解码显示。此图可以是刚才传输给网络任务模块的图象或是刚从网络上得到的图象。解码完成后,如果设置标注网格,处理任务模块在图象上标注网格。通过发送一个SCOM 消息,输出的图象接着发送给输出任务。(C)输出任务。输出任务将图象显示在显示设备上。它使用输出驱动程序提供的FVID_exchange 调用实现图象的显示。它得到的图象的格式是YUV 4:2:0 的,需要重新采样成YUV 4:2:2 格式。然后等待处理任务发来的消息以继续运行。(D)控制任务。控制任务管理可选参数,可以控制JPEG 图象帧率和压缩质量。控制任务检测参数的改变,这些参数定义在一个全局结构“External Control”,同时将更新的参数复制到任务自定义的结构“External Control_prev”中,并向处理任务模块的邮箱中发送消息。处理任务模块定时检测这些消息并调用相应单元的控制函数。(E)网络初始化任务。网络初始化任务启动网络环境。当网络准备好后,建立网络任务。(F)网络任务网络任务用于支持系统中的网络功能调用。当它初始化完成后,它开始监听两个端口(3001 和3002)。3001 端口用于“回放”连接,当客户端希望发送视频流给DSP。端口3002 用于“记录”连接,当客户端希望从DSP 接收视频流。网络任务模块接着等待一个从处理模块发来的SCOM 消息,其中应包含可供使用的新的JPEG 图象。首先,网络模块用发来的JPEG 图象在RAM 中建立一个可由HTTP 服务器识别和可发送到HTTP 客户端的图象文件(IMAGE1.JPG)当一个“记录”连接激活时,网络模块首先检测是否客户端发送过来一些命令。命令包含设置日期和时间、是否显示日期和时间、是否显示网格在输出图象上。然后,接收的JPEG 图象要进行活动检测。如果图象有改变,则发送图象到“记录”连接上。否则发送空文件指示以使客户端的图象保持同步。下一步,如果一个“播放”连接被激活,从连接中得到一个新的JPEG 图象。这个新的图象就替代处理模块发来的图象。网络模块回传JPEG 图象给处理模块,通过发送一个SCOM 消息。

三.调试与结论。

本系统在美国TI公司提供的集成开发环境CCS2.2版本下调试通过,它对于安防监控领域有着广阔的应用前景。

本文创新点:采用面向媒体处理的专用DSP来开发网络视频服务器,其开发时间不长,优点是由于算法是软件代码,所以可以不断对产品性能进行升级,重复开发成本较低。TI的CCS编译器已进行了充分的优化,再加上DSP本身的强大处理能力,对于一般的处理算法,只要用标准C语言编写就可以达到应用的需求。但是对于视频服务器,一般有多路图像的输入,这时编码速度越快,就意味着可以处理更多路的输入图像,也就意味着更高的产品性价比,因此充分发挥DM642的最高性能是本文的另一创新点。

参 考 文 献:

1.TMS320DM642 Video/Imaging Fixed-Point Digital Signal processor Data Manual (SPRS200)

2.TMS320C64x DSP Video Port/VCXO Interpolated Control (VIC) Port Reference Guide (SPRU629)

3. 丁媛媛,石中锁.基于MPEG-4的嵌入式网络视频服务器的设技. 微计算机信息.2004.12 :61-63

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论