浅谈四层板和33欧电阻

选用四层板不仅是电源和地的问题,高速数字电路对走线的阻抗有要求,二层板不好控制阻抗。33欧电阻一般加在驱动器端,也是起阻抗匹配作用的;布线时要先布数据地址线,和需要保证的高速线。

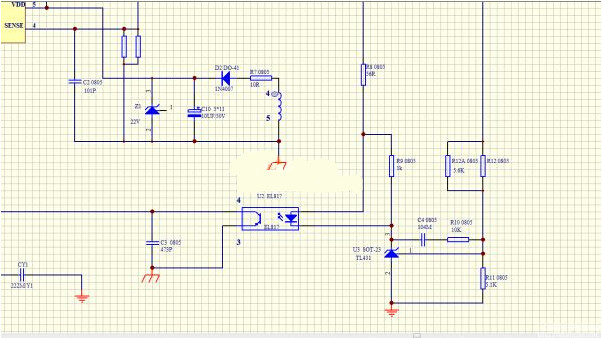

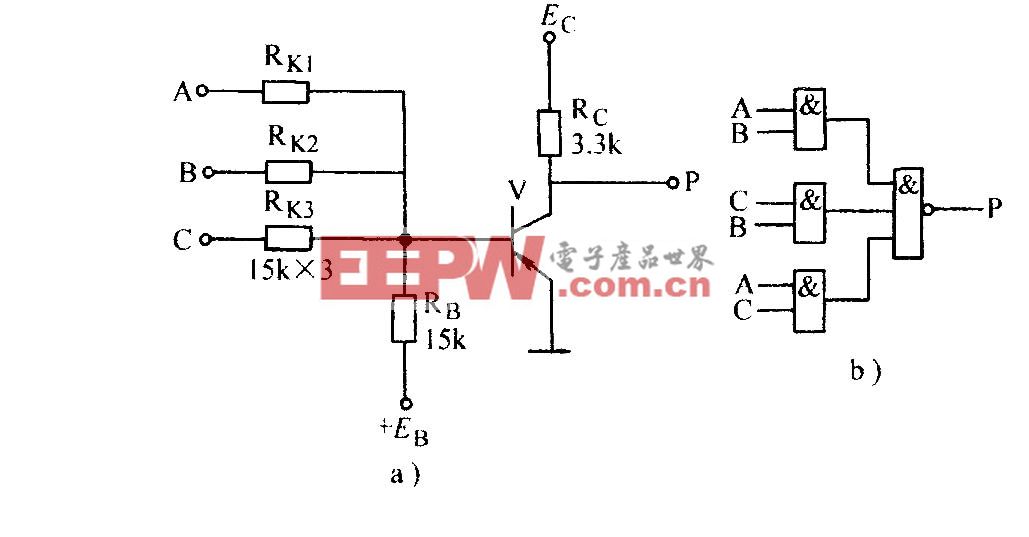

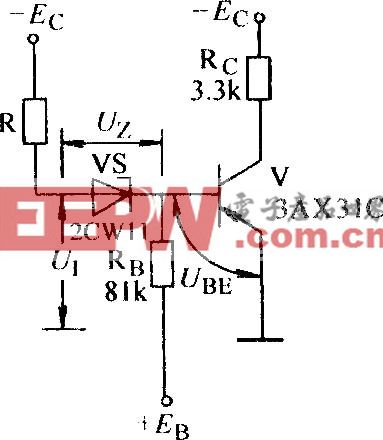

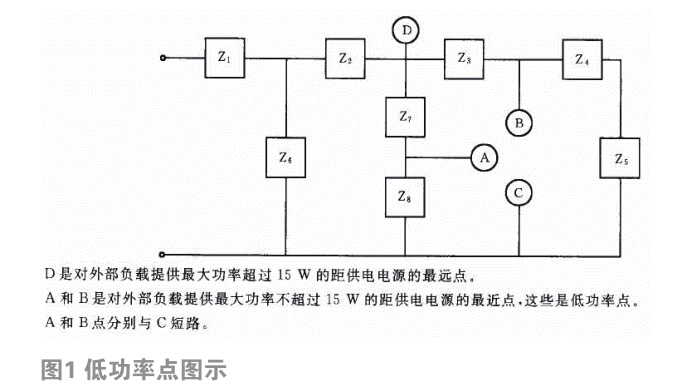

在高频的时候,PCB板上的走线都要看成传输线。传输线有其特征阻抗,学过传输线理论的都知道,当传输线上某处出现阻抗突变(不匹配)时,信号通过就会发生反射,反射对原信号造成干扰,严重时就会影响电路的正常工作。采用四层板时,通常外层走信号线,中间两层分别为电源和地平面,这样一方面隔离了两个信号层,更重要的是外层的走线与它们所靠近的平面形成称为“微带”(microstrip) 的传输线,它的阻抗比较固定,而且可以计算。对于两层板就比较难以做到这样。这种传输线阻抗主要于走线的宽度、到参考平面的距离、敷铜的厚度以及介电材料的特性有关,有许多现成的公式和程序可供计算。

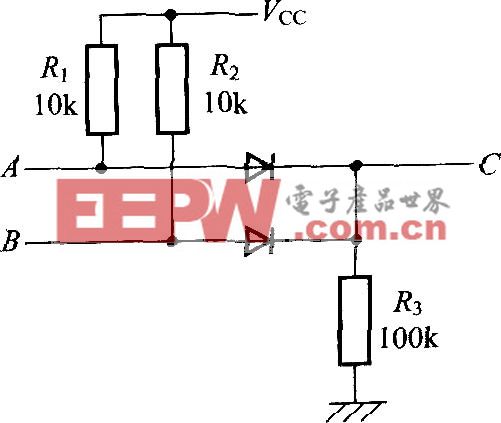

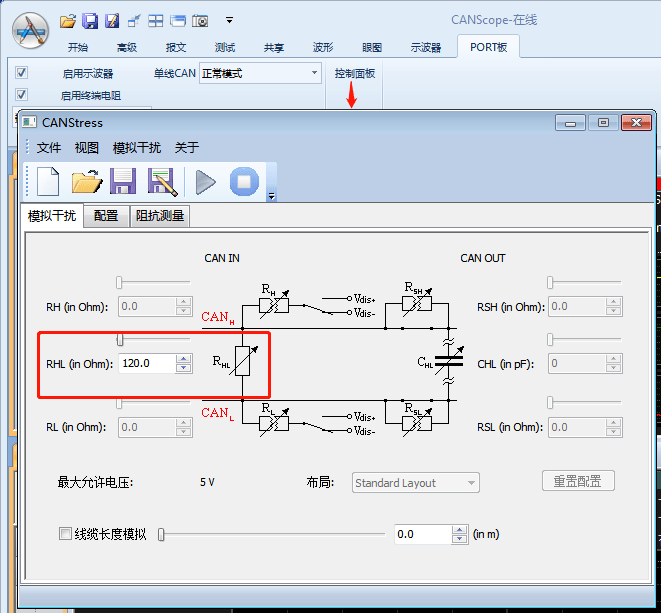

33欧电阻通常串连放在驱动的一端(其实不一定33欧,从几欧到五、六十欧都有,视电路具体情况) ,其作用是与发送器的输出阻抗串连后与走线的阻抗匹配,使反射回来(假设解收端阻抗没有匹配) 的信号不会再次反射回去(吸收掉),这样接收端的信号就不会受到影响。接收端也可以作匹配,例如采用电阻并联,但在数字系统比较少用,因为比较麻烦,而且很多时候是一发多收,如地址总线,不如源端匹配易做。

这里所说的高频,不一定是时钟频率很高的电路,是不是高频不止看频率,更重要是看信号的上升下降时间。通常可以用上升(或下降) 时间估计电路的频率,一般取上升时间倒数的一半,比如如果上升时间是1ns,那么它的倒数是1000MHz,也就是说在设计电路是要按500MHz的频带来考虑。有时候要故意减慢边缘时间,许多高速IC其驱动器的输出斜率是可调的

光敏电阻相关文章:光敏电阻工作原理

评论