SOPC技术在电力机车改造中的应用

引 言

机车逻辑控制模块(LCM)是一种铁路机车专用的采用硬件可编程的逻辑控制单元,是机车实时监测与故障诊断系统的一个CAN网络节点。将该模块与整个系统应用在干线电力机车上,实现了传统的继电器控制电路的可编程无触点控制,大大减少了控制电路的触点和布线,简化了机车控制电路的设计、生产和调试过程,并使机车电气系统具有实时检测、故障诊断与存储显示等功能;特别是列车速度提高后,继电器电路因振动加剧而出现误动作,无触点逻辑控制模块可以方便地克服该缺点,提高控制系统可靠性,并可方便地用硬件描述语言实现各种控制功能,具有灵活性和通用性。无触点控制是机车电气控制系统的发展方向。

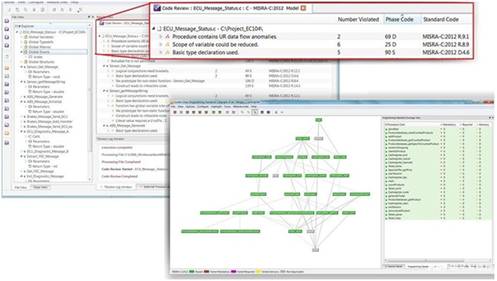

图1所示为机车实时监测与故障诊断系统示意图。

随着系统集成技术不断成熟,出现了IP(IntellectualProperty,知识产权)产品及模块化设计。在集成电路设计中,IP特指可以通过知识产权贸易在各设计公司间流通的实现特定功能的电路模块。IP核的本质特征是可重用性,通常满足良好的通用性、良好的可移植性及绝对正确三个基本特征,是未来SOPC设计的核心。要使SOPC设计成功,就要更多地采用知识产权(IP)复用,以快速完成设计,得到价格低廉的硅器件,从而满足市场需求。

本设计主要针对韶山3型4000系电力机车控制逻辑进行分析优化,并设计了可以完全取代原有逻辑控制功能的IP核;在此基础上利用SOPC技术设计了机车逻辑控制模块。

1 机车逻辑控制模块简介

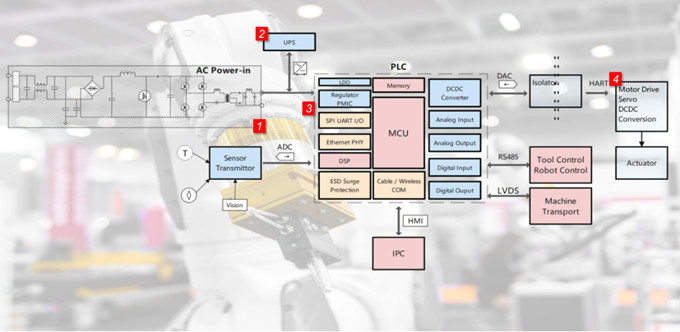

主要针对韶山3型4000系电力机车设计的逻辑控制模块,借鉴了以往在韶山4G型电力机车上应用的设计经验,在状态采集(输入)电路、驱动(输出)电路、保护电路、冗余设计以及逻辑处理方面都做了一定改进。尤其是在逻辑处理部分大量采用现代集成技术和模块化的设计方法,优化了控制逻辑,进一步提高了集成度和可靠性,其原理如图2所示。

逻辑控制模块将控制指令信息通过采集电路输入,经过逻辑处理后驱动执行机构,并将当前状态信息通过CAN总线发送到司机显示屏。

2 逻辑替代的基本原理

获取继电器的状态即通过检测与继电器关联的线号的得失电状态,经过与之对应的逻辑组合得出继电器是否得电;得到的继电器状态构成继电器状态表,供后级电路查询。以最基本的自锁连接的中间继电器来说明,其示意图如图3所示,替代后的虚拟继电器如图4所示。

替代后的中间继电器采用通用的模块化设计。在具体应用过程中只要调用这些继电器模块,按原继电器连接信号进行端口定义就可以方便的使用。自锁连接的继电器功能仿真如图5所示,其端口定义和Verilog HDL实现如下:

对于时间继电器,在输出级根据继电器状态表里的状态信息,通过对外部输入脉冲的计数来达到延时动作的目的。这种处理方式得到的延迟时间精度高,状态稳定。以零位时间继电器为例说明其一般替代原理。其继电器原理如图6所示,替代后的虚拟继电器如图7所示。

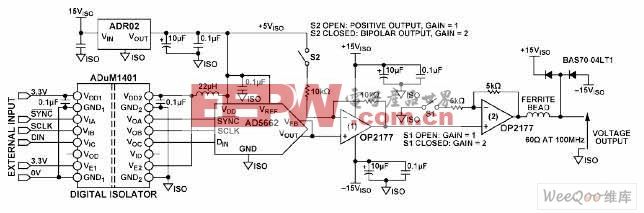

同样,时间继电器采用通用的模块化设计,虚拟的继电器可以直观地理解为实际继电器模型;按照实际继电器接线对其进行信号端口定义就可以完全取代原有继电器逻辑,最终得到的输出信号输送给调制模块进行100 kHz方波调制输出给隔离变压器。时间继电器功能仿真如图8所示,其端口定义和Verilog HDL实现如下:

逻辑控制IP核实现

作为可重用的设计模块,IP核必须遵从一定的互连接口标准,包括Altera在内的很多公司都有自己的一套互连接口的标准,像Altera公司的Avalon、Atlantic,IBM公司的CoreConnect,ARM公司的AMBA,还有SiliCore转让给OpenCore的WISHBONE总线标准等。Avalon交换式总线是由Altera公司开发的一种专用内部连线技术。Avalon交换式总线由SOPC Builder自动生成,是一种最理想的用于系统处理器和外设之间的内联总线。每当一个新的组件被添加到系统中或是某个外设的优先级被改变,就会有一个新的、最佳的交换式总线被生成。

采用Altera公司开发的Avalon交互式片上系统总线作为本IP核的内联总线,连接各个模块。其结构框图如图9所示,包括数字滤波器模块、逻辑管理模块、继电器状态生成模块、输出状态生成模块和输出脉冲调制模块。逻辑控制单元IP核内共有3个Avalon从端口由片内处理器内核控制总线上的数据流传输,实现各个模块的协同工作。

逻辑控制单元IP替代原有继电器控制逻辑,司机控制指令经过分压电路、光耦隔离以及施密特触发器后进入FPGA。为避免尖峰干扰造成的误触发,在IP核中增加了数字滤波器。通过滤波器的信号被认为是真正的司机指令,按照原有的控制功能,进行逻辑处理并产生虚拟的继电器状态表。该状态表在传输给输出级逻辑模块的同时可以接受Avalon总线访问。输出级根据继电器状态进行逻辑处理,产生输出状态表。该状态表经过脉冲调制后作为隔离变压器原边驱动信号传送至输出驱动电路门极。

4 逻辑控制IP核基础上设计逻辑控制模块

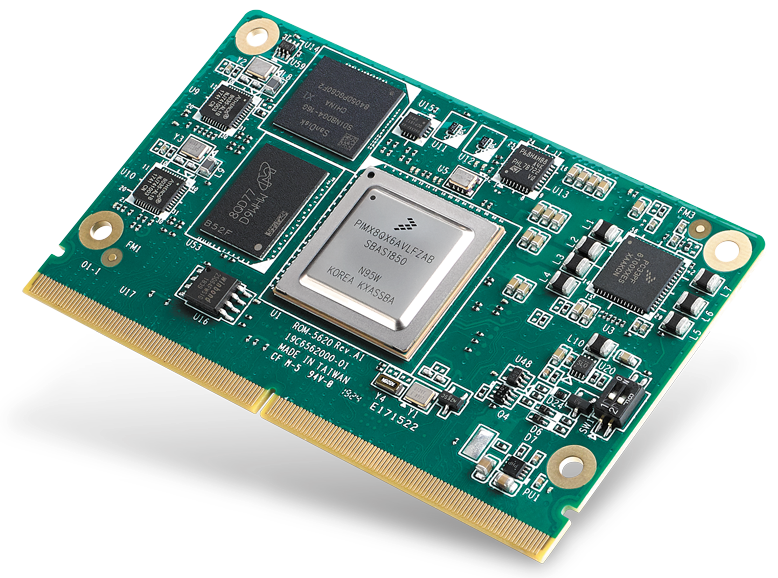

Altera公司的Quarters II开发平台提供了电子设计的软硬件协同开发环境。逻辑控制模块硬件设计如图10所示。系统采用Avalon总线为系统总线,以32位NiosII微处理器作为主控制器。本设计在SOPC Builder开发环境下直接调用片内的M4K块并设置一个从端口生成系统内存,调用逻辑控制单元IP以及Altera提供的CAN通信控制器IP实现LCM与CAN总线的接口。

由司机控制指令生成的虚拟继电器状态表在被传送至输出级的同时,可以被片内Nios微处理器查询。查询的过程是通过芯片内部Avalon总线进行的,得到的查询结果由CAN总线传送到显示屏和检测仪。

5 系统综合

在完成IP设计的基础上,利用SOPC Builder进行系统综合。FPGA内部用Avalon总线将片上处理器和外设连接成片上系统,如图11所示。

在设计中,包含了由Nios CPU、JTAG以及片上存储器构成的基本片上系统。在此基础上调用SS3LCM与CAN接口控制器IP实现逻辑控制及通信功能。另外增加了一个串行接口,方便与上位机连接测试。综合后得到的芯片结构如图12所示。

评论