双极性集成电路的ESD保护

——

摘要: 描述了IC的ESD保护方案。

关键词: ESD保护;双极集成电路

概述

集成电路需要抗静电保护电路,一些保护电路是内置的,一些保护措施则来自具体的应用电路。为了正确保护IC,需要考虑以下内容:

*对IC造成ESD的传递模式

*IC内部的ESD保护电路

*应用电路与IC内部ESD保护的相互配合

*修改应用电路提高IC的ESD保护能力

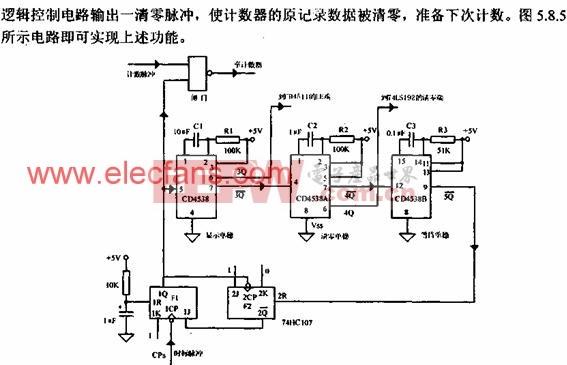

IC内部的ESD保护可以阻止传递到芯片内部敏感电路的较高能量,内部钳位二极管用于保护IC免受过压冲击。应用电路的外部去耦电容可将ESD电压限制在安全水平。然而,小容量的去耦电容可能影响IC的保护电路。如果使用小去耦电容,通常需要外部ESD电压钳位二极管。

ESD传递模式

ESD电平用电压描述,这个电压源于与IC相连的电容上的储存电荷。一般不会考虑有上千伏的电压作用于IC。为了评估传递给IC的能量,需要一个模拟放电模型的测试装置。

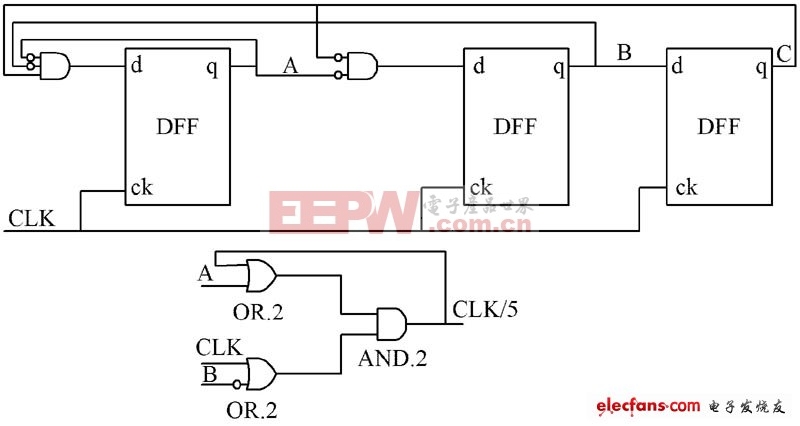

ESD测试中一般使用两种充电模式(图1),人体模式(HBM)下将电荷储存在人体模型(100pF等效电容)中,通过人体皮肤放电(1.5kW等效电阻)。机器模式(MM)下将电荷储存在金属物体,机器模式中的放电只受内部连接电感的限制。

图1 ESD测试模型

以下概念对于评估集成电路内部的ESD传递非常有用:

1. 对于高于标称电源的电压来说,IC阻抗较低。

IESD=VESD/Z ZHBM=1.5kW

2. 在机器模式下,电流受特征阻抗(约50W)的限制。

ZMM=V/I=肔/C0

低阻能量损耗:

E=1/2 C0

评论